RM0033 Rev 9 849/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

28.4.4 MII/RMII selection

The mode, MII or RMII, is selected using the configuration bit 23, MII_RMII_SEL, in the

SYSCFG_PMC register. The application has to set the MII/RMII mode while the Ethernet

controller is under reset or before enabling the clocks.

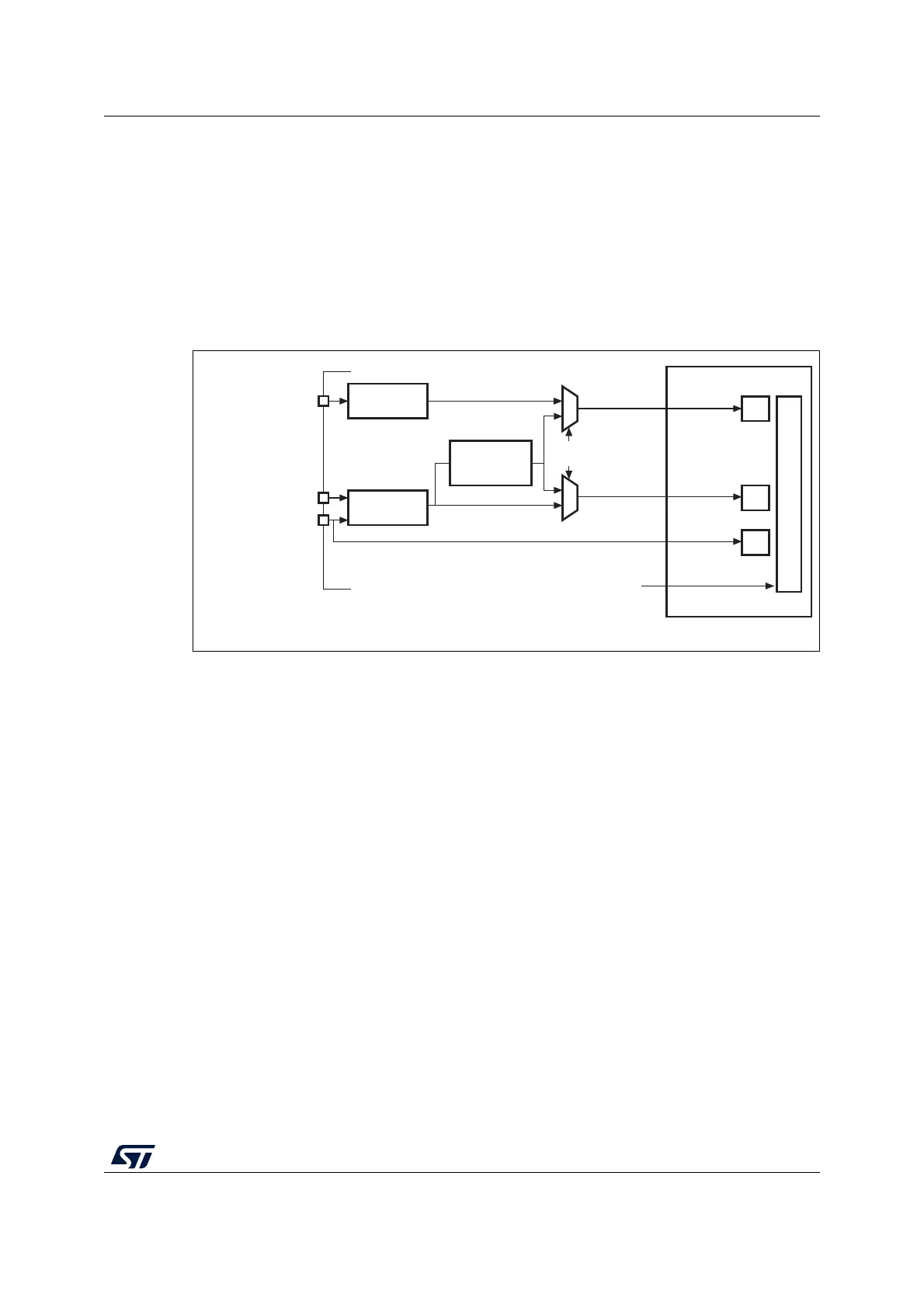

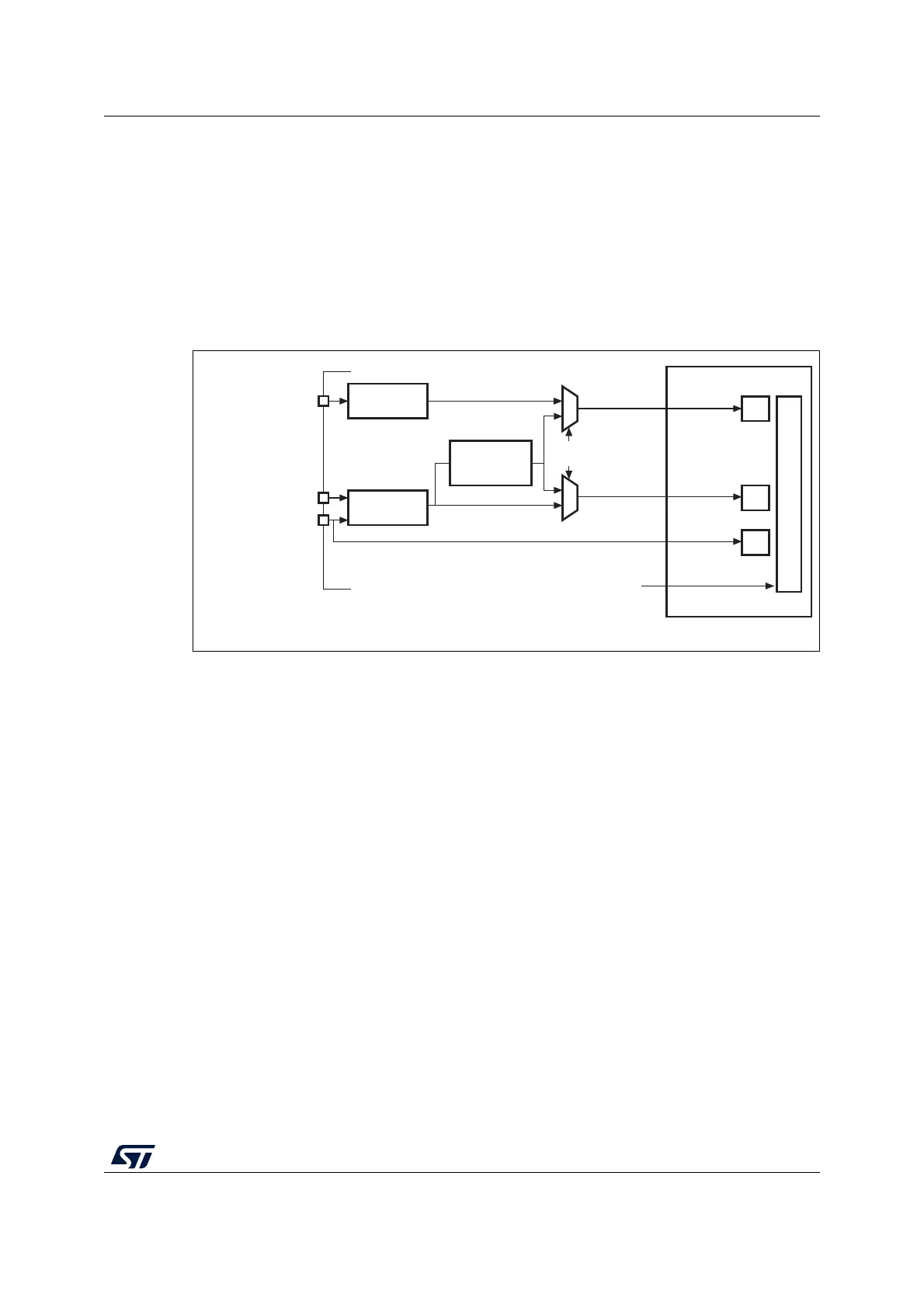

MII/RMII internal clock scheme

The clock scheme required to support both the MII and RMII, as well as 10 and 100 Mbit/s

operations is described in Figure 321.

Figure 321. Clock scheme

1. The MII/RMII selection is controlled through bit 23, MII_RMII_SEL, in the SYSCFG_PMC register.

To save a pin, the two input clock signals, RMII_REF_CK and MII_RX_CLK, are multiplexed

on the same GPIO pin.

28.5 Ethernet functional description: MAC 802.3

The IEEE 802.3 International Standard for local area networks (LANs) employs the

CSMA/CD (carrier sense multiple access with collision detection) as the access method.

The Ethernet peripheral consists of a MAC 802.3 (media access control) controller with

media independent interface (MII) and a dedicated DMA controller.

The MAC block implements the LAN CSMA/CD sublayer for the following families of

systems: 10 Mbit/s and 100 Mbit/s of data rates for baseband and broadband systems. Half-

and full-duplex operation modes are supported. The collision detection access method is

applied only to the half-duplex operation mode. The MAC control frame sublayer is

supported.

GPIO and AF

controller

GPIO and AF

controller

MII_TX_CLK as AF

(25 MHz or 2.5 MHz)

MII_RX_CLK as AF

(25 MHz or 2.5 MHz)

Sync. divider

/2 for 100 Mb/s

/20 for 10 Mb/s

50 MHz

0

1

0

1

25 MHz or 2.5 MHz

25 MHz or 2.5 MHz

0 MII

1 RMII

(1)

25 MHz

or 2.5 MHz

25 MHz

or 2.5 MHz

MACTXCLK

MACRXCLK

TX

RX

AHB

HCLK

HCLK

MAC

must be greater

than 25 MHz

ai15650

RMII

RMII_REF_CK as AF

(50 MHz)

Loading...

Loading...