RM0033 Rev 9 861/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

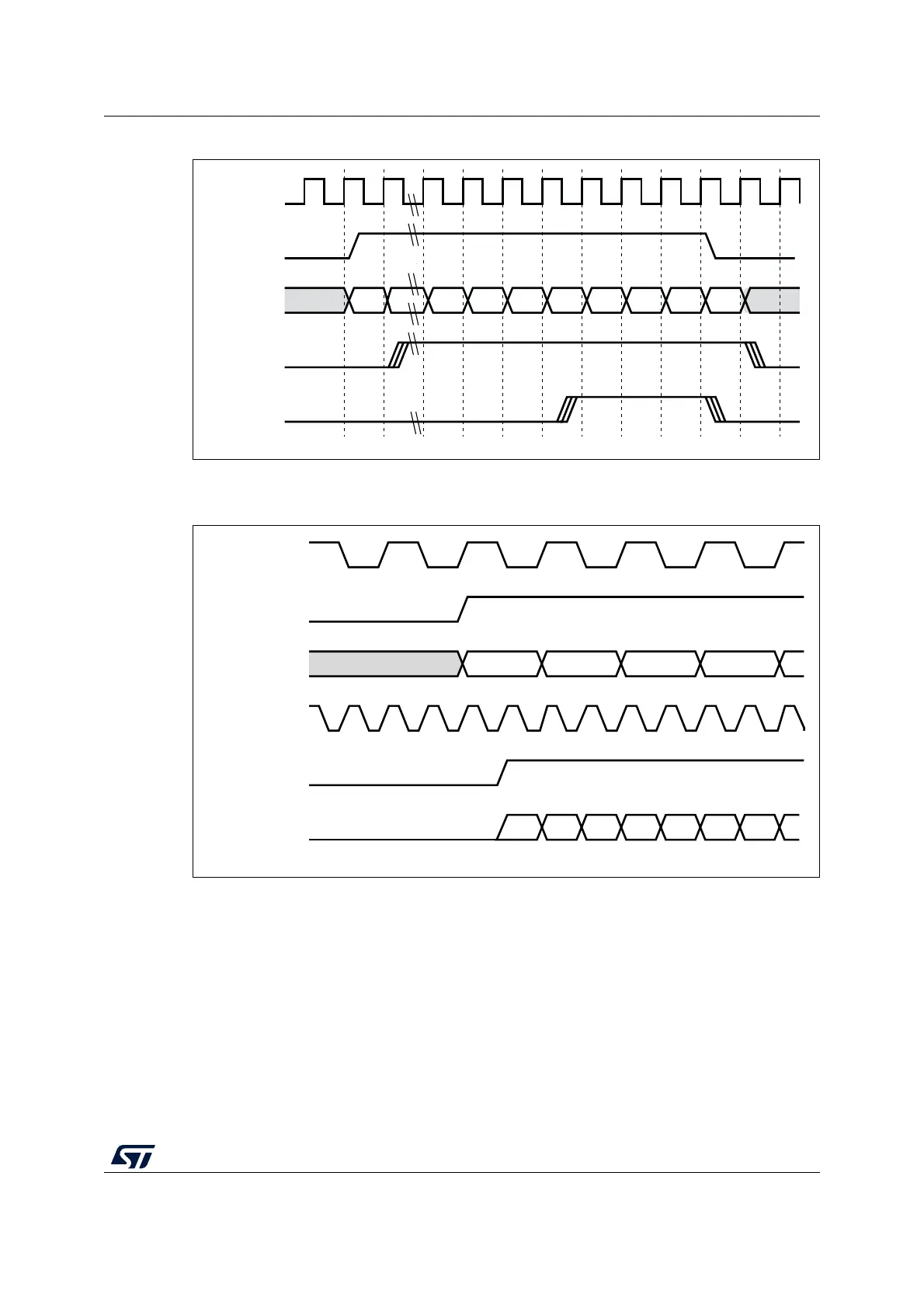

Figure 327. Transmission with collision

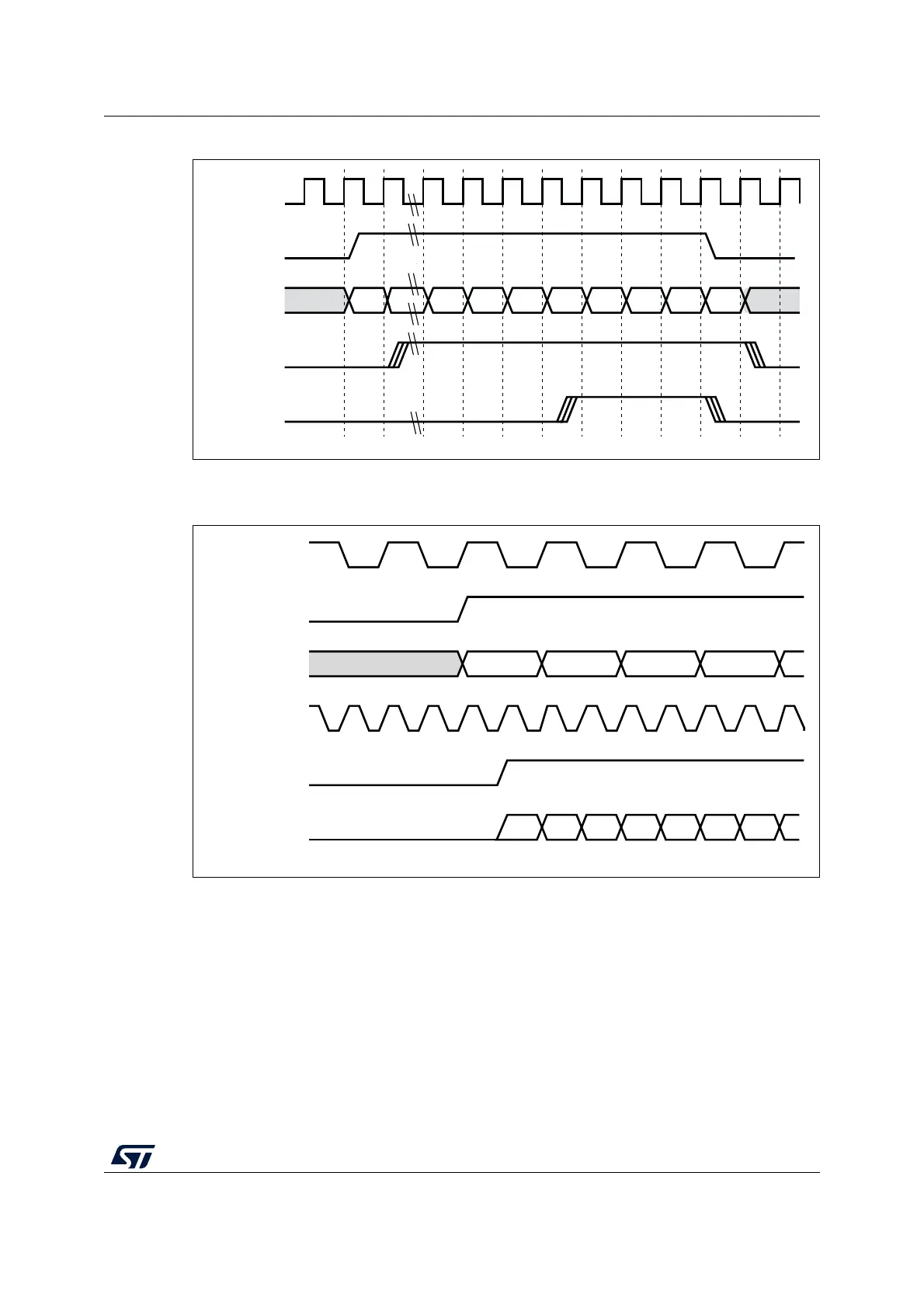

Figure 328 shows a frame transmission in MII and RMII.

Figure 328. Frame transmission in MMI and RMII modes

28.5.3 MAC frame reception

The MAC received frames are pushes into the Rx FIFO. The status (fill level) of this FIFO is

indicated to the DMA once it crosses the configured receive threshold (RTC in the

ETH_DMAOMR register) so that the DMA can initiate pre-configured burst transfers

towards the AHB interface.

In the default Cut-through mode, when 64 bytes (configured with the RTC bits in the

ETH_DMAOMR register) or a full packet of data are received into the FIFO, the data are

popped out and the DMA is notified of its availability. Once the DMA has initiated the

transfer to the AHB interface, the data transfer continues from the FIFO until a complete

MII_TX_CLK

MII_TX_EN

MII_TXD[3:0]

PR EAM BLE SFD

MII_CS

MII_COL

ai15651

DA DA JAM JAM JAM JAM

MII_RX_CLK

MII_TX_EN

MII_TXD[3:0]

RMII_REF_CLK

RMII_TXD[1:0]

RMII_TX_EN

ai15652

Loading...

Loading...