DMA controller (DMA) RM0033

188/1381 RM0033 Rev 9

Note: Peripheral port may be the source or the destination (it could also be the memory source in

the case of memory-to-memory transfer).

PSIZE, MSIZE and NDT[15:0] have to be configured so as to ensure that the last transfer

will not be incomplete. This can occur when the data width of the peripheral port (PSIZE

bits) is lower than the data width of the memory port (MSIZE bits). This constraint is

summarized in Table 27.

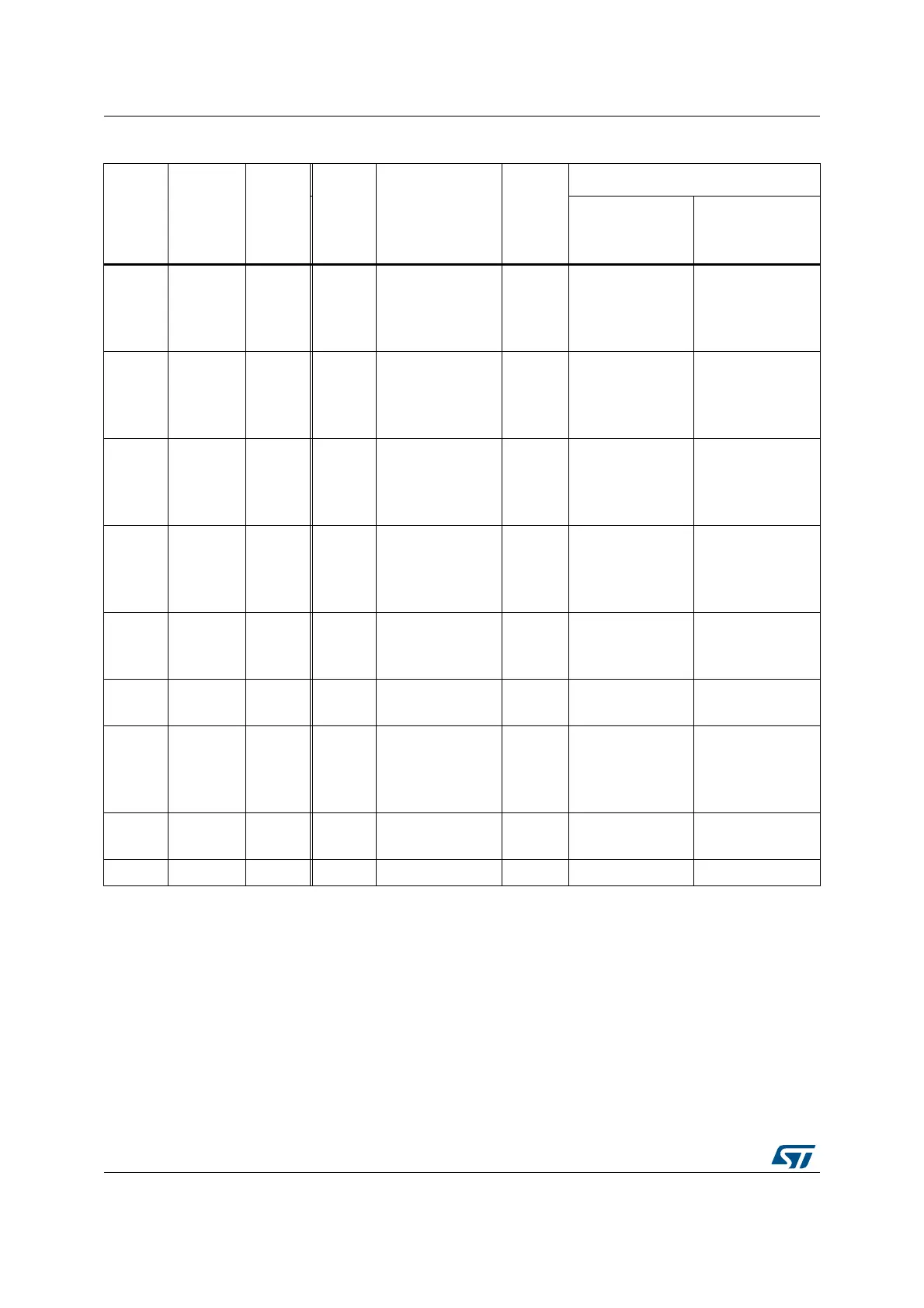

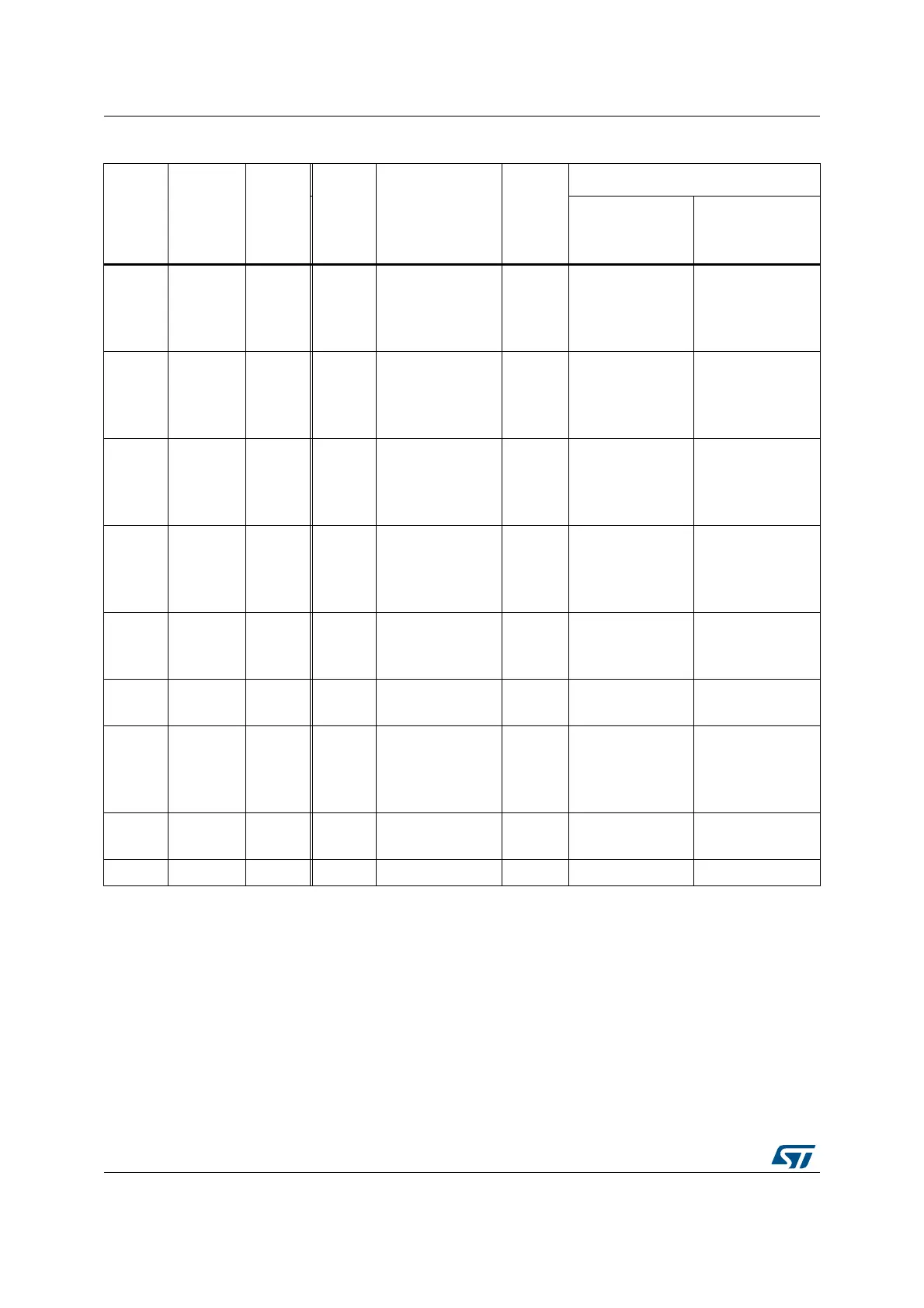

Table 26. Packing/unpacking & endian behavior (bit PINC = MINC = 1)

AHB

memory

port

width

AHB

peripheral

port width

Number

of data

items to

transfer

(NDT)

-

Memory

transfer

number

Memory port

address / byte

lane

Peripher

al

transfer

number

Peripheral port address / byte lane

- PINCOS = 1 PINCOS = 0

88 4-

1

2

3

4

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

1

2

3

4

0x0 / B0[7:0]

0x4 / B1[7:0]

0x8 / B2[7:0]

0xC / B3[7:0]

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

816 2

-

1

2

3

4

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

1

2

0x0 / B1|B0[15:0]

0x4 / B3|B2[15:0]

0x0 / B1|B0[15:0]

0x2 / B3|B2[15:0]

832 1

-

1

2

3

4

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

1

0x0 / B3|B2|B1|B0[31:0] 0x0 / B3|B2|B1|B0[31:0]

16 8 4

-

1

2

0x0 / B1|B0[15:0]

0x2 / B3|B2[15:0]

1

2

3

4

0x0 / B0[7:0]

0x4 / B1[7:0]

0x8 / B2[7:0]

0xC / B3[7:0]

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

16 16 2

-

1

2

0x0 / B1|B0[15:0]

0x2 / B1|B0[15:0]

1

2

0x0 / B1|B0[15:0]

0x4 / B3|B2[15:0]

0x0 / B1|B0[15:0]

0x2 / B3|B2[15:0]

16 32 1

-

1

2

0x0 / B1|B0[15:0]

0x2 / B3|B2[15:0]

1

0x0 / B3|B2|B1|B0[31:0] 0x0 / B3|B2|B1|B0[31:0]

32 8 4

-

1

0x0 / B3|B2|B1|B0[31:0]

1

2

3

4

0x0 / B0[7:0]

0x4 / B1[7:0]

0x8 / B2[7:0]

0xC / B3[7:0]

0x0 / B0[7:0]

0x1 / B1[7:0]

0x2 / B2[7:0]

0x3 / B3[7:0]

32 16 2

-

1

0x0 /B3|B2|B1|B0[31:0]

1

2

0x0 / B1|B0[15:0]

0x4 / B3|B2[15:0]

0x0 / B1|B0[15:0]

0x2 / B3|B2[15:0]

32 32 1

- 1 0x0 /B3|B2|B1|B0 [31:0] 1 0x0 /B3|B2|B1|B0 [31:0] 0x0 / B3|B2|B1|B0[31:0]

Loading...

Loading...