General-purpose timers (TIM2 to TIM5) RM0033

380/1381 RM0033 Rev 9

does not change). In addition, if the URS bit (update request selection) in TIMx_CR1

register is set, setting the UG bit generates an update event UEV but without setting the UIF

flag (thus no interrupt or DMA request is sent). This is to avoid generating both update and

capture interrupts when clearing the counter on the capture event.

When an update event occurs, all the registers are updated and the update flag (UIF bit in

TIMx_SR register) is set (depending on the URS bit):

• The buffer of the prescaler is reloaded with the preload value (content of the TIMx_PSC

register)

• The auto-reload shadow register is updated with the preload value (TIMx_ARR)

The following figures show some examples of the counter behavior for different clock

frequencies when TIMx_ARR=0x36.

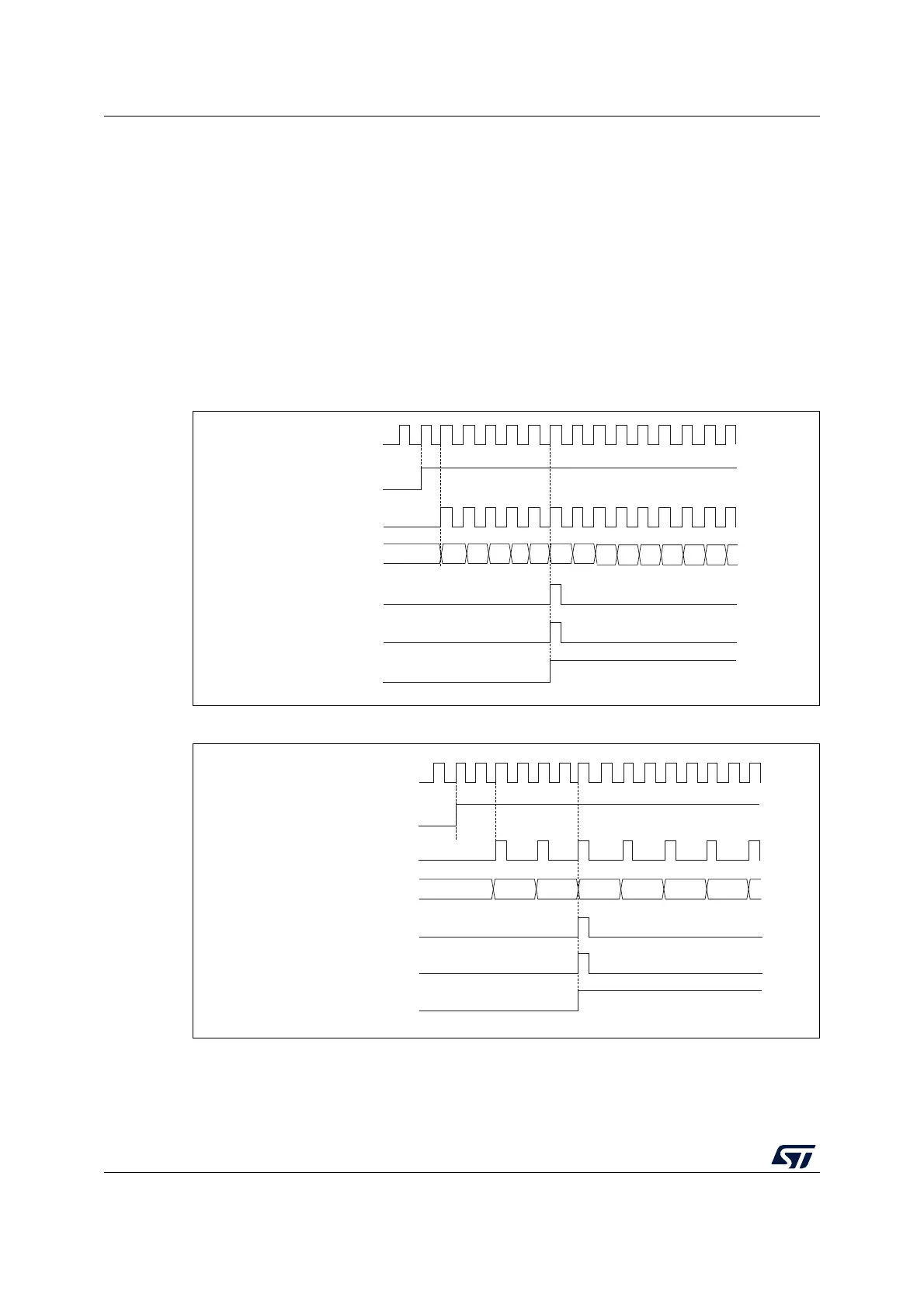

Figure 116. Counter timing diagram, internal clock divided by 1

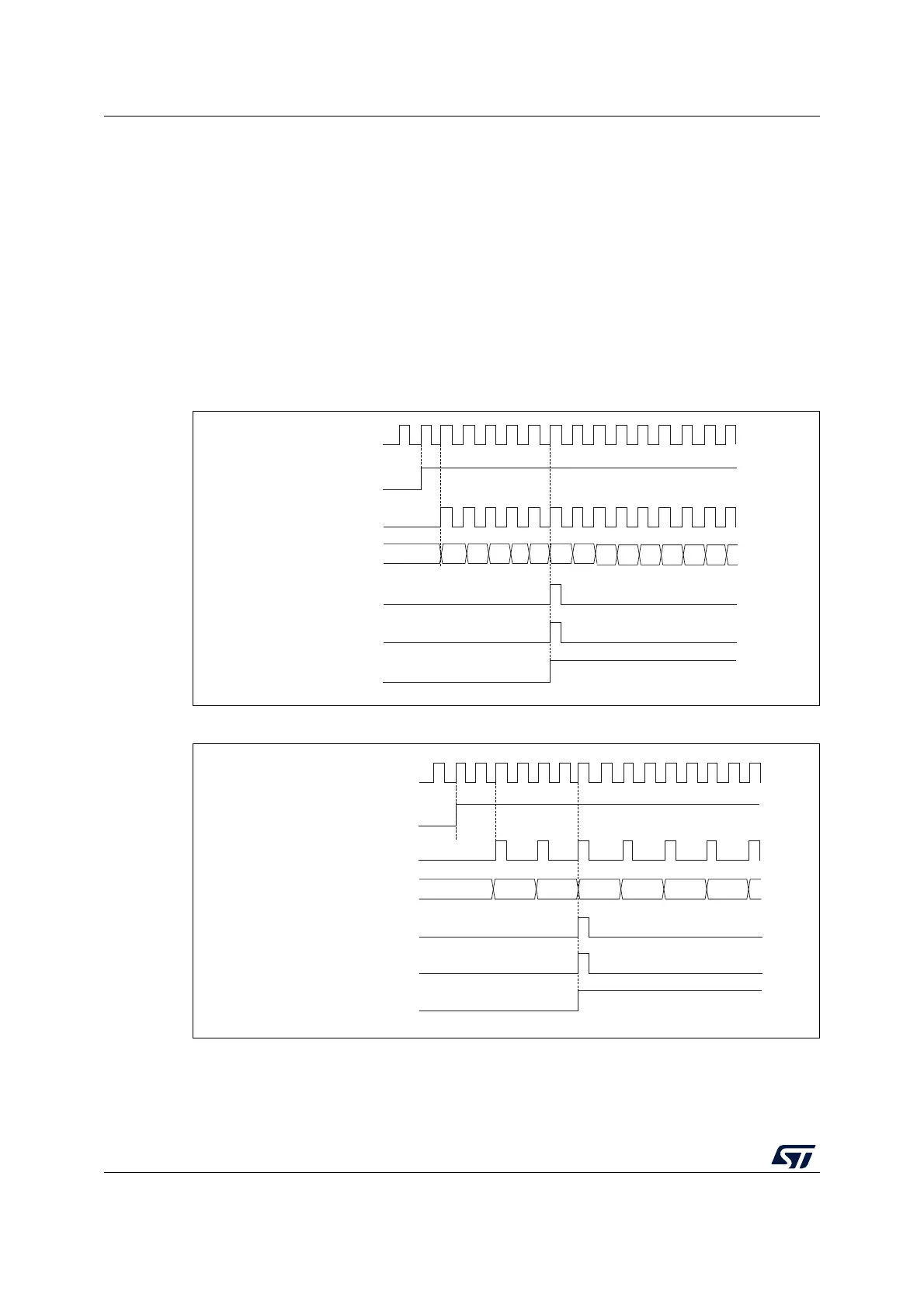

Figure 117. Counter timing diagram, internal clock divided by 2

00 02 03 04 05 06 0733 34 35 3631

MS35836V1

CK_INT

CNT_EN

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag (UIF)

0132

MS35835V1

CK_INT

CNT_EN

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag (UIF)

0034 0035 0036 0000 0001 0002 0003

Loading...

Loading...