RM0033 Rev 9 847/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

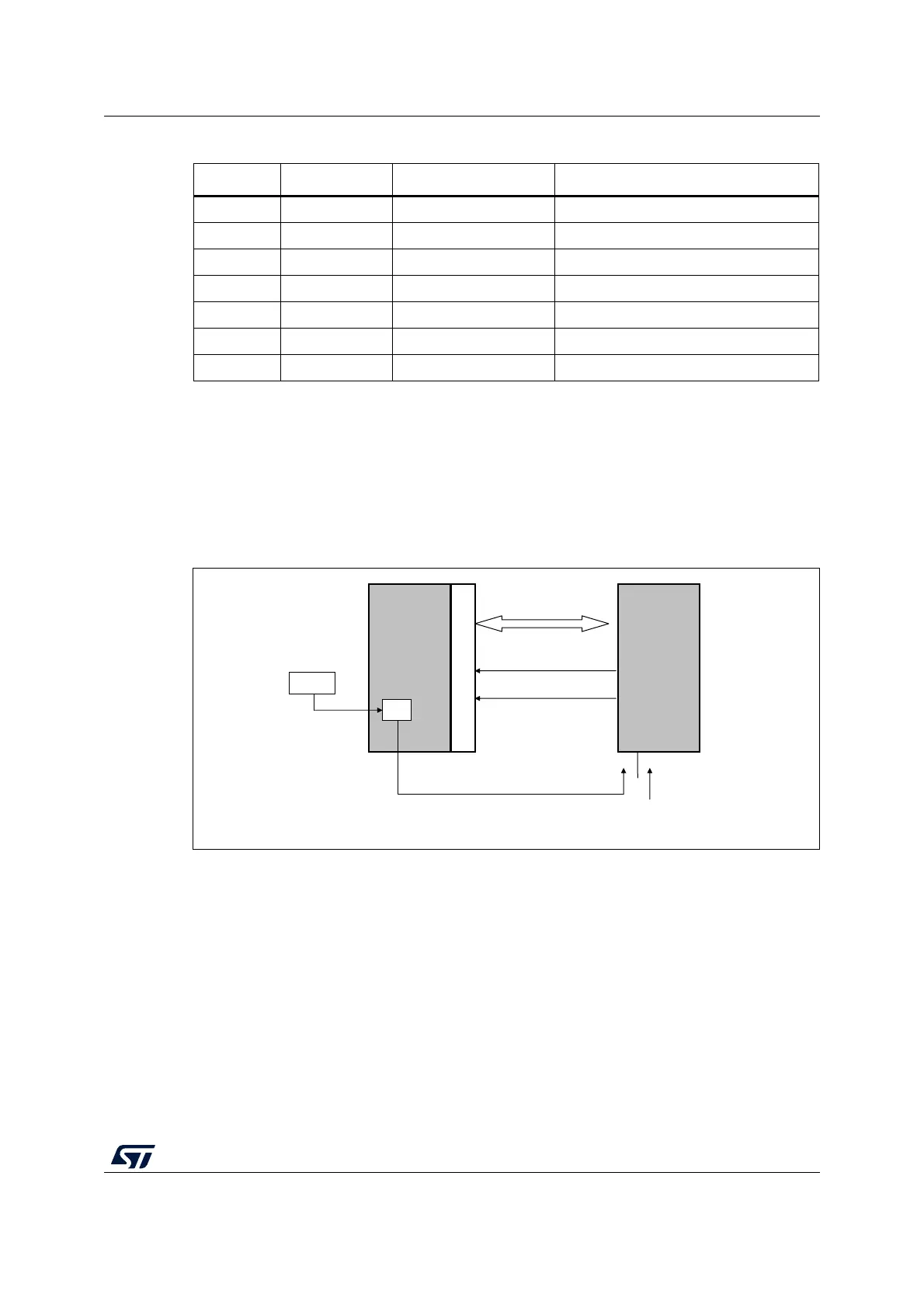

MII clock sources

To generate both TX_CLK and RX_CLK clock signals, the external PHY must be clocked

with an external 25 MHz as shown in Figure 318. Instead of using an external 25 MHz

quartz to provide this clock, the STM32F20x and STM32F21xmicrocontroller can output this

signal on its MCO pin. In this case, the PLL multiplier has to be configured so as to get the

desired frequency on the MCO pin, from the 25 MHz external quartz.

Figure 318. MII clock sources

28.4.3 Reduced media-independent interface: RMII

The reduced media-independent interface (RMII) specification reduces the pin count

between the microcontroller Ethernet peripheral and the external Ethernet in 10/100 Mbit/s.

According to the IEEE 802.3u standard, an MII contains 16 pins for data and control. The

RMII specification is dedicated to reduce the pin count to 7 pins (a 62.5% decrease in pin

count).

Table 142. RX interface signal encoding

MII_RX_DV MII_RX_ERR MII_RXD[3:0] Description

0 0 0000 through 1111 Normal inter-frame

0 1 0000 Normal inter-frame

0 1 0001 through 1101 Reserved

0 1 1110 False carrier indication

0 1 1111 Reserved

1 0 0000 through 1111 Normal data reception

1 1 0000 through 1111 Data reception with errors

STM32

MCU

MCO

25 MHz

25 MHz

TX _CLK

For 10/100 Mbit/s

RX _CLK

HSE

802.3 MAC

ai15623b

External

PHY

Loading...

Loading...