Ethernet (ETH): media access control (MAC) with DMA controller RM0033

848/1381 RM0033 Rev 9

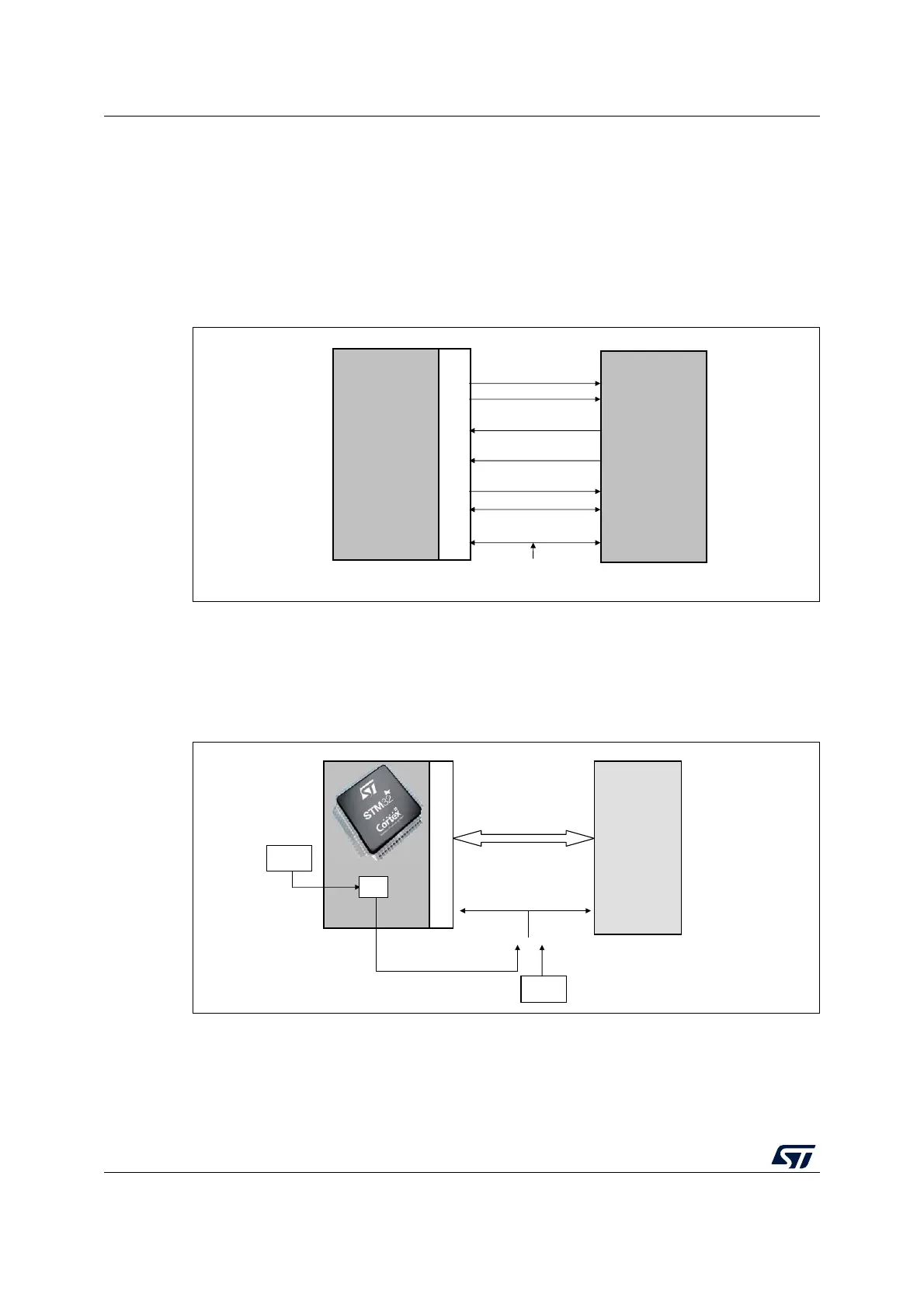

The RMII is instantiated between the MAC and the PHY. This helps translation of the MAC’s

MII into the RMII. The RMII block has the following characteristics:

• It supports 10-Mbit/s and 100-Mbit/s operating rates

• The clock reference must be doubled to 50 MHz

• The same clock reference must be sourced externally to both MAC and external

Ethernet PHY

• It provides independent 2-bit wide (dibit) transmit and receive data paths

Figure 319. Reduced media-independent interface signals

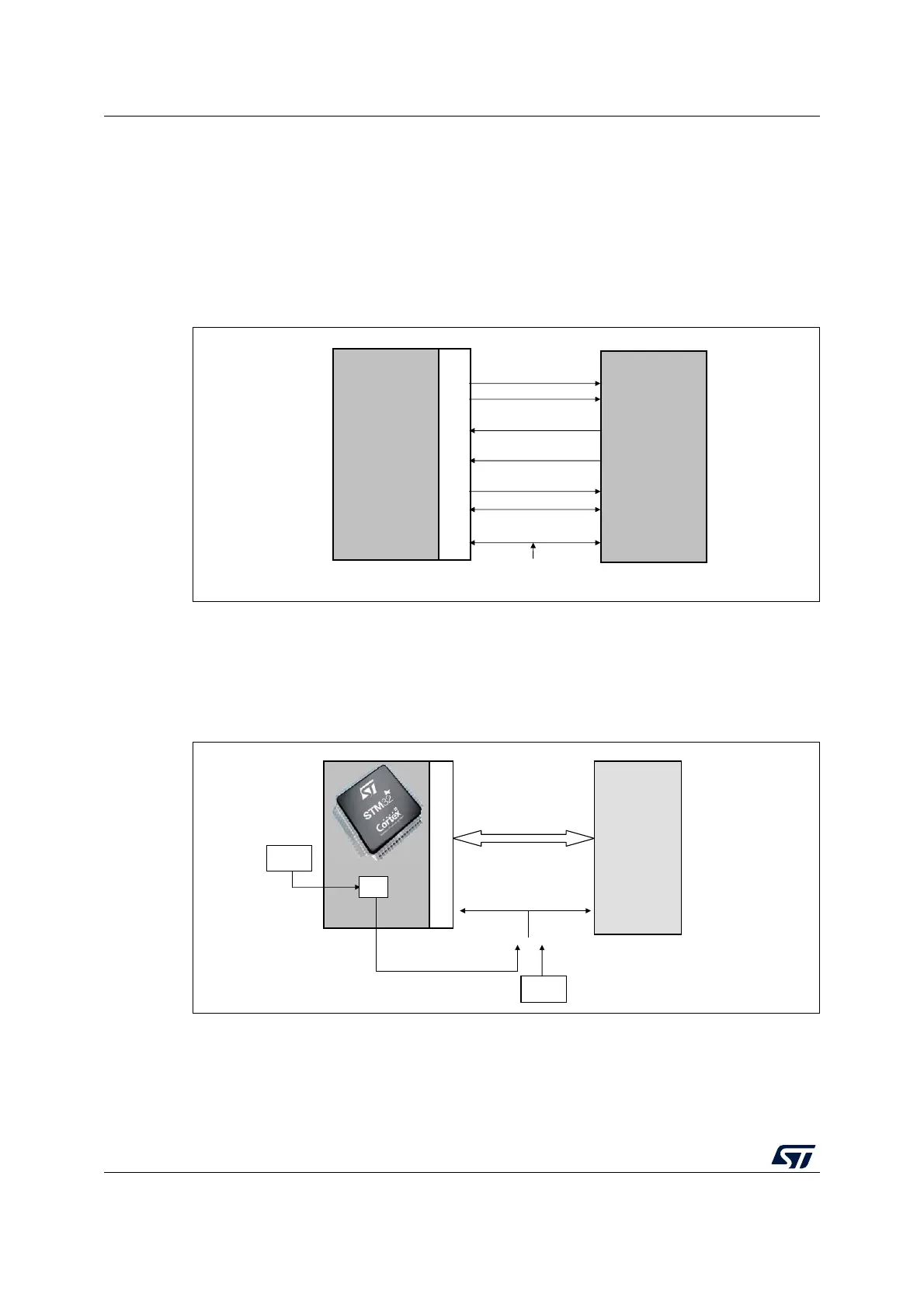

RMII clock sources

As described in the RMII clock sources section, the STM32F20x and

STM32F21xSTM32F107xx could provide this 50 MHz clock signal on its MCO output pin

and you then have to configure this output value through PLL configuration.

Figure 320. RMII clock sources

STM32

MCU

TXD[1:0]

TX_EN

RXD[1:0]

CRS_DV

MDC

MDIO

REF_ CLK

Clock source

802.3 MAC

External

PHY

ai15624b

STM32

REF_CLK

50 MHz

50 MHz

MCO

25 MHz

PLL

For 10/100 Mbit/s

External

PHY

ai1562

802.3 MAC

Loading...

Loading...