RM0033 Rev 9 397/1381

RM0033 General-purpose timers (TIM2 to TIM5)

436

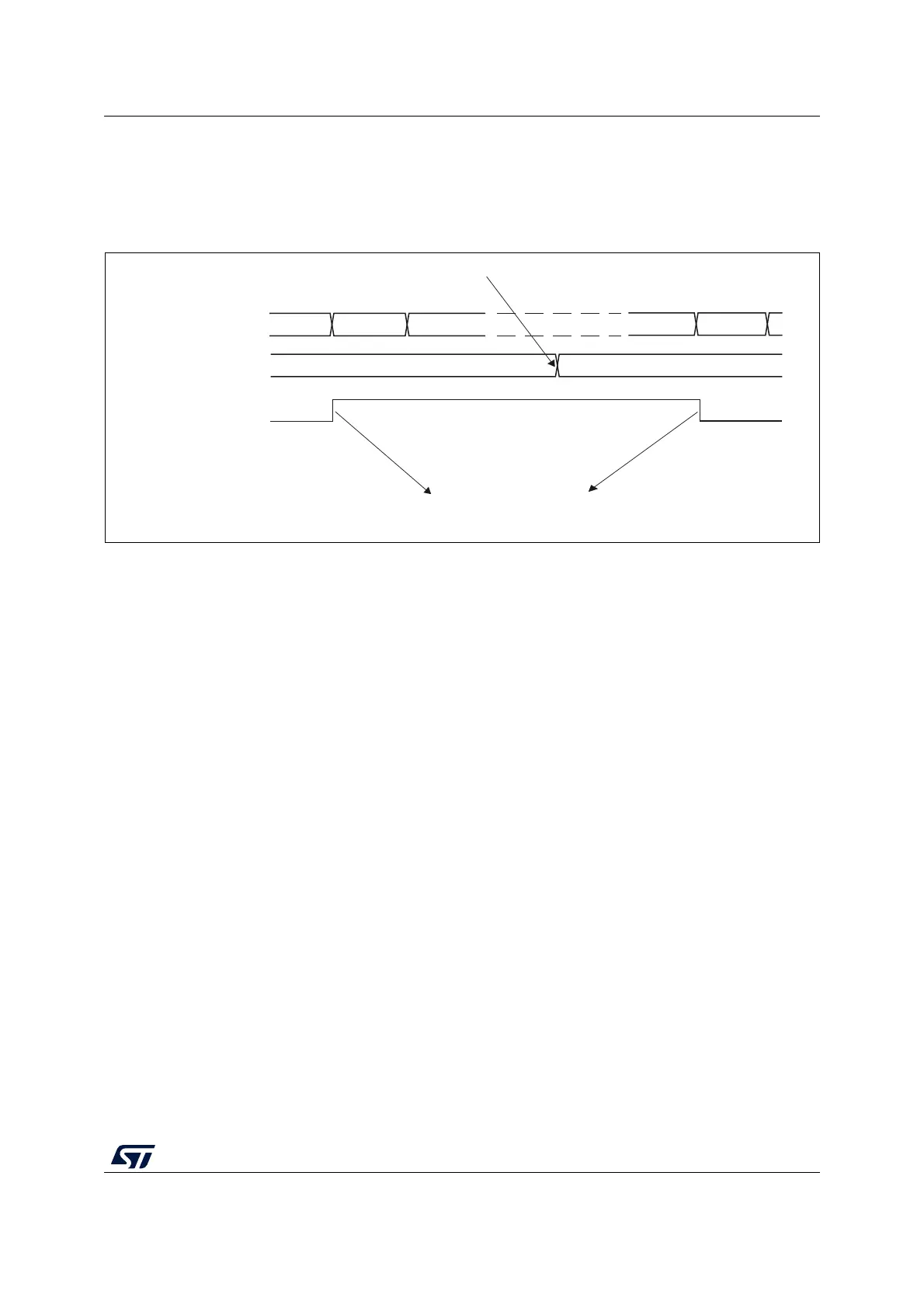

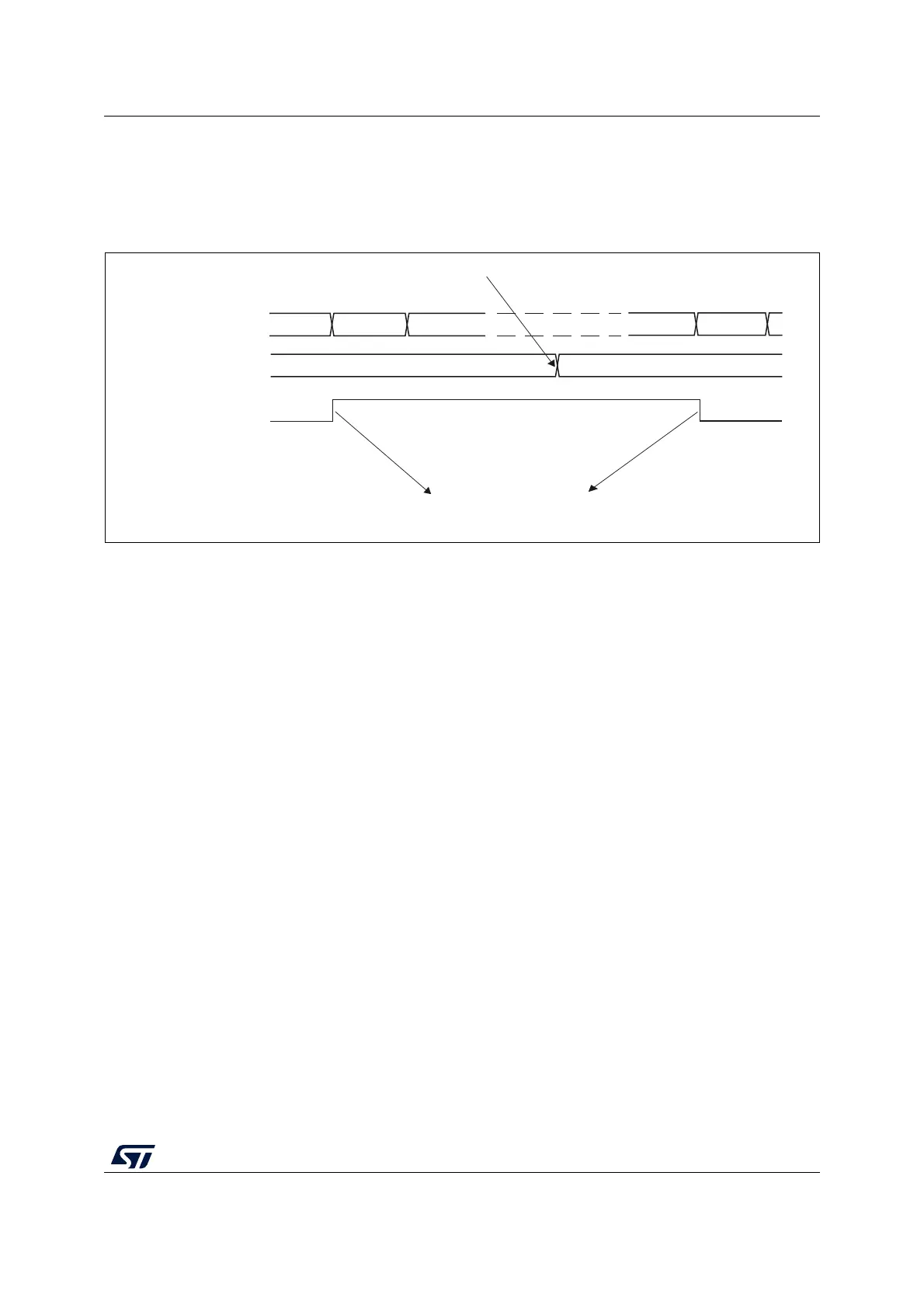

The TIMx_CCRx register can be updated at any time by software to control the output

waveform, provided that the preload register is not enabled (OCxPE=0, else TIMx_CCRx

shadow register is updated only at the next update event UEV). An example is given in

Figure 142.

Figure 142. Output compare mode, toggle on OC1

14.3.9 PWM mode

Pulse width modulation mode allows generating a signal with a frequency determined by the

value of the TIMx_ARR register and a duty cycle determined by the value of the

TIMx_CCRx register.

The PWM mode can be selected independently on each channel (one PWM per OCx

output) by writing 110 (PWM mode 1) or ‘111 (PWM mode 2) in the OCxM bits in the

TIMx_CCMRx register. The user must enable the corresponding preload register by setting

the OCxPE bit in the TIMx_CCMRx register, and eventually the auto-reload preload register

by setting the ARPE bit in the TIMx_CR1 register.

As the preload registers are transferred to the shadow registers only when an update event

occurs, before starting the counter, the user has to initialize all the registers by setting the

UG bit in the TIMx_EGR register.

OCx polarity is software programmable using the CCxP bit in the TIMx_CCER register. It

can be programmed as active high or active low. OCx output is enabled by the CCxE bit in

the TIMx_CCER register. Refer to the TIMx_CCERx register description for more details.

In PWM mode (1 or 2), TIMx_CNT and TIMx_CCRx are always compared to determine

whether TIMx_CCRx≤ TIMx_CNT or TIMx_CNT≤ TIMx_CCRx (depending on the direction

of the counter). However, to comply with the ETRF (OCREF can be cleared by an external

event through the ETR signal until the next PWM period), the OCREF signal is asserted

only:

• When the result of the comparison changes, or

• When the output compare mode (OCxM bits in TIMx_CCMRx register) switches from

the “frozen” configuration (no comparison, OCxM=‘000) to one of the PWM modes

(OCxM=‘110 or ‘111).

This forces the PWM by software while the timer is running.

MS37363V1

OC1REF = OC1

TIMx_CNT

B200 B2010039

TIMx_CCR1

003A

Write B201h in the CC1R register

Match detected on CCR1

Interrupt generated if enabled

003B

B201

003A

Loading...

Loading...