Universal synchronous asynchronous receiver transmitter (USART) RM0033

638/1381 RM0033 Rev 9

Idle characters

Setting the TE bit drives the USART to send an idle frame before the first data frame.

24.3.3 Receiver

The USART can receive data words of either 8 or 9 bits depending on the M bit in the

USART_CR1 register.

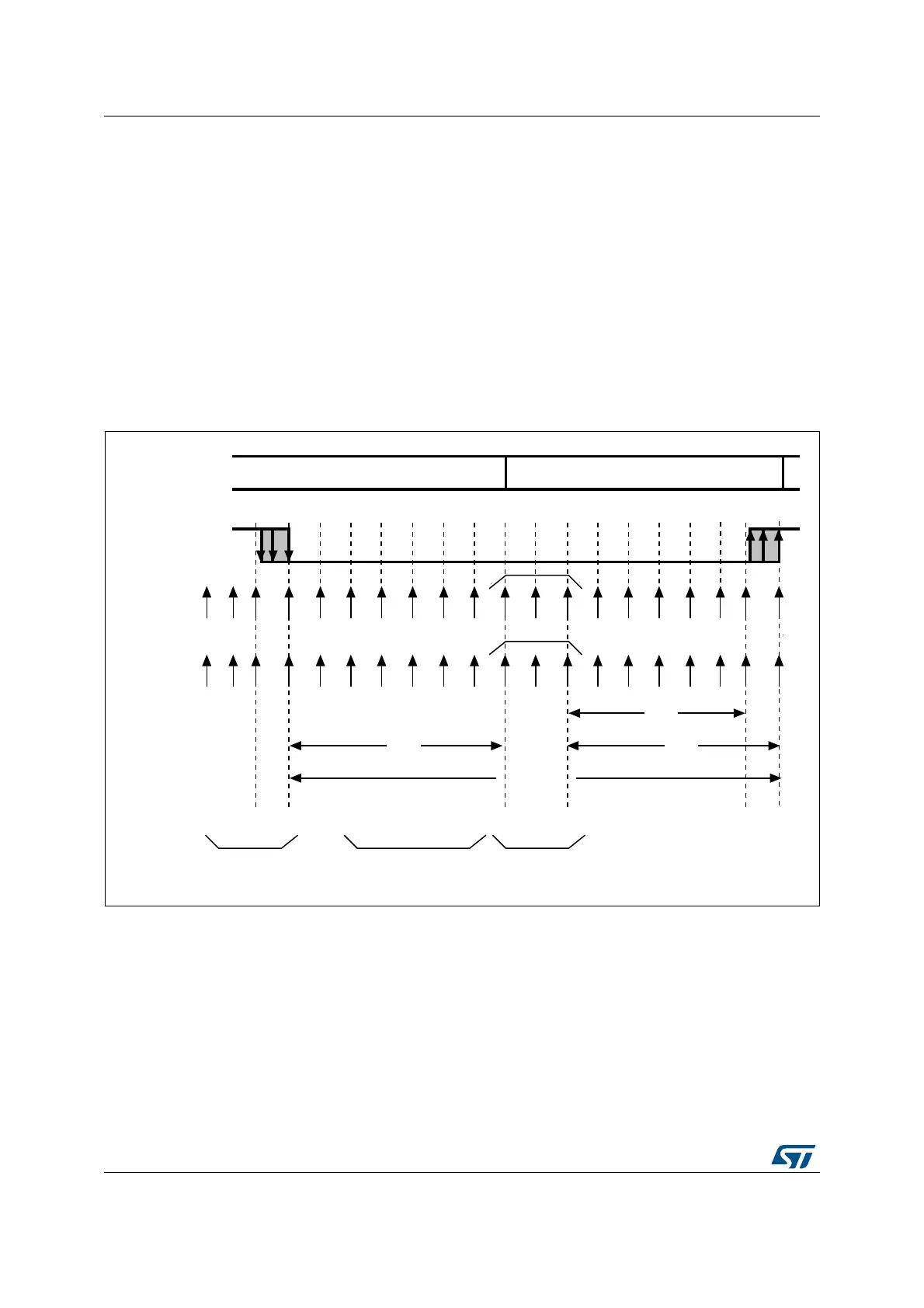

Start bit detection

The start bit detection sequence is the same when oversampling by 16 or by 8.

In the USART, the start bit is detected when a specific sequence of samples is recognized.

This sequence is: 1 1 1 0 X 0 X 0 X 0 0 0 0.

Figure 227. Start bit detection when oversampling by 16 or 8

Note: If the sequence is not complete, the start bit detection aborts and the receiver returns to the

idle state (no flag is set) where it waits for a falling edge.

The start bit is confirmed (RXNE flag set, interrupt generated if RXNEIE=1) if the 3 sampled

bits are at 0 (first sampling on the 3rd, 5th and 7th bits finds the 3 bits at 0 and second

sampling on the 8th, 9th and 10th bits also finds the 3 bits at 0).

The start bit is validated (RXNE flag set, interrupt generated if RXNEIE=1) but the NE noise

flag is set if, for both samplings, at least 2 out of the 3 sampled bits are at 0 (sampling on the

01 0 X0 X 000 0 X XXXXX

Falling edge

detection

11

1 2 3 4 5 6 7 8 9 10 111213141516

X X X X X X X X 9 10 111213141516

6/16

7/167/16

X

At least 2 bits

out of 3 at 0

At least 2 bits

out of 3 at 0

One-bit time

Conditions

to validate

the start bit

Real

sample

clock

Ideal

sample

clock

RX line

RX state

Idle

Start bit

Sampled values

ai15471b

Loading...

Loading...