RM0033 Rev 9 249/1381

RM0033 Analog-to-digital converter (ADC)

255

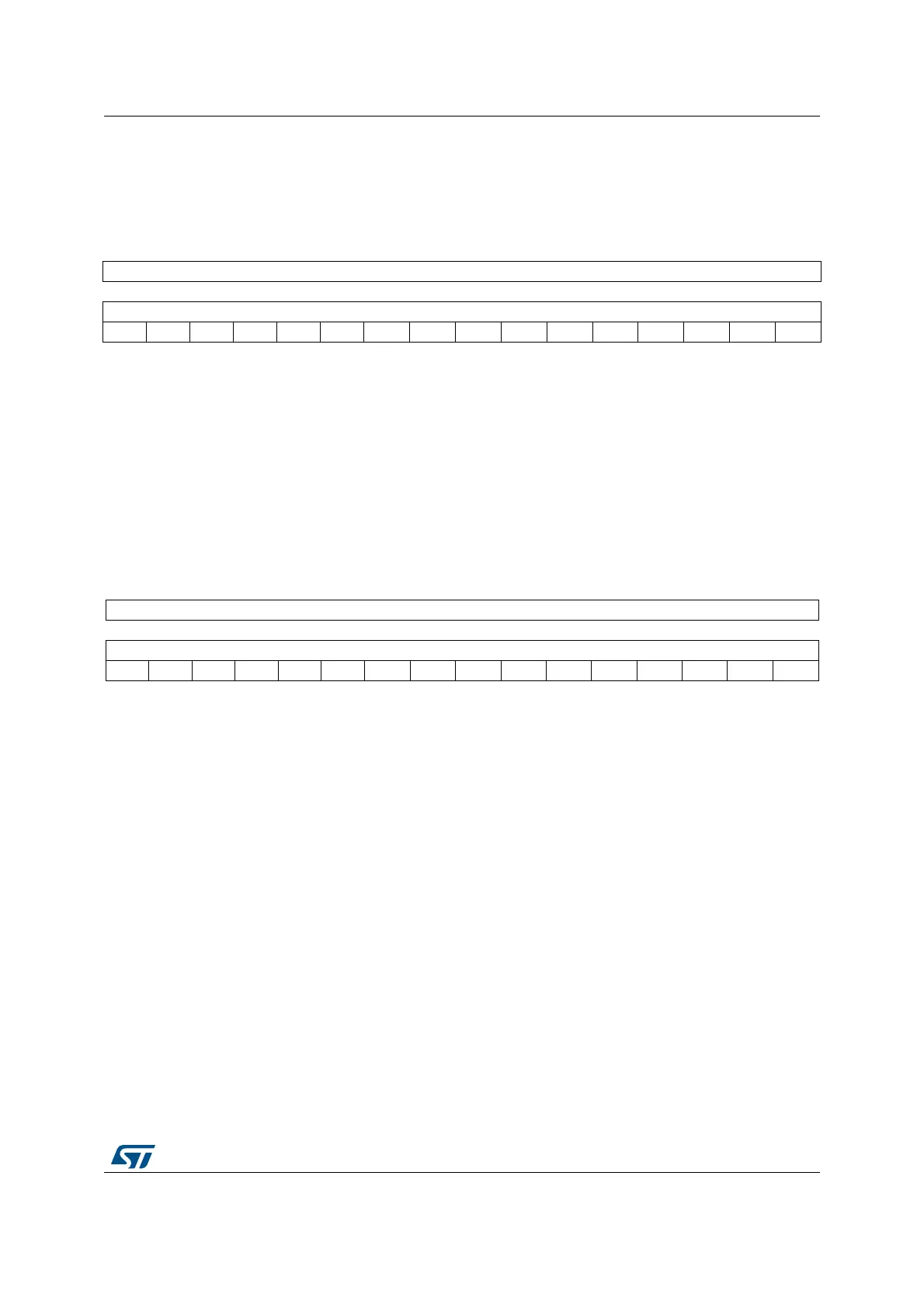

10.13.13 ADC injected data register x (ADC_JDRx) (x= 1..4)

Address offset: 0x3C - 0x48

Reset value: 0x0000 0000

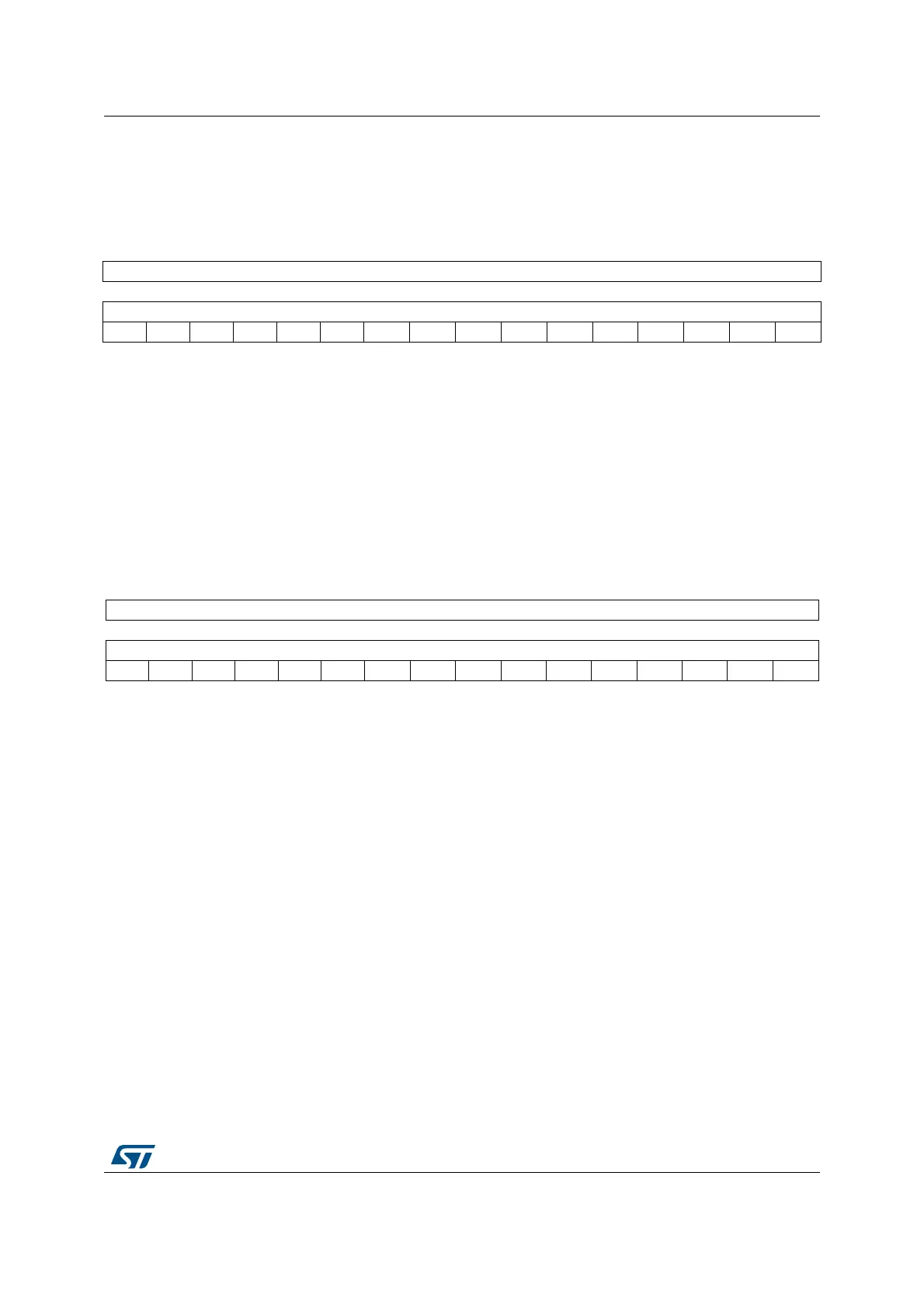

10.13.14 ADC regular data register (ADC_DR)

Address offset: 0x4C

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

JDATA[15:0]

rrrrrr r r r r rrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 JDATA[15:0]: Injected data

These bits are read-only. They contain the conversion result from injected channel x. The

data are left -or right-aligned as shown in Figure 32 and Figure 33.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA[15:0]

rrrrrrr r r r r r r r r r

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 DATA[15:0]: Regular data

These bits are read-only. They contain the conversion result from the regular

channels. The data are left- or right-aligned as shown in Figure 32 and

Figure 33.

Loading...

Loading...