General-purpose timers (TIM2 to TIM5) RM0033

408/1381 RM0033 Rev 9

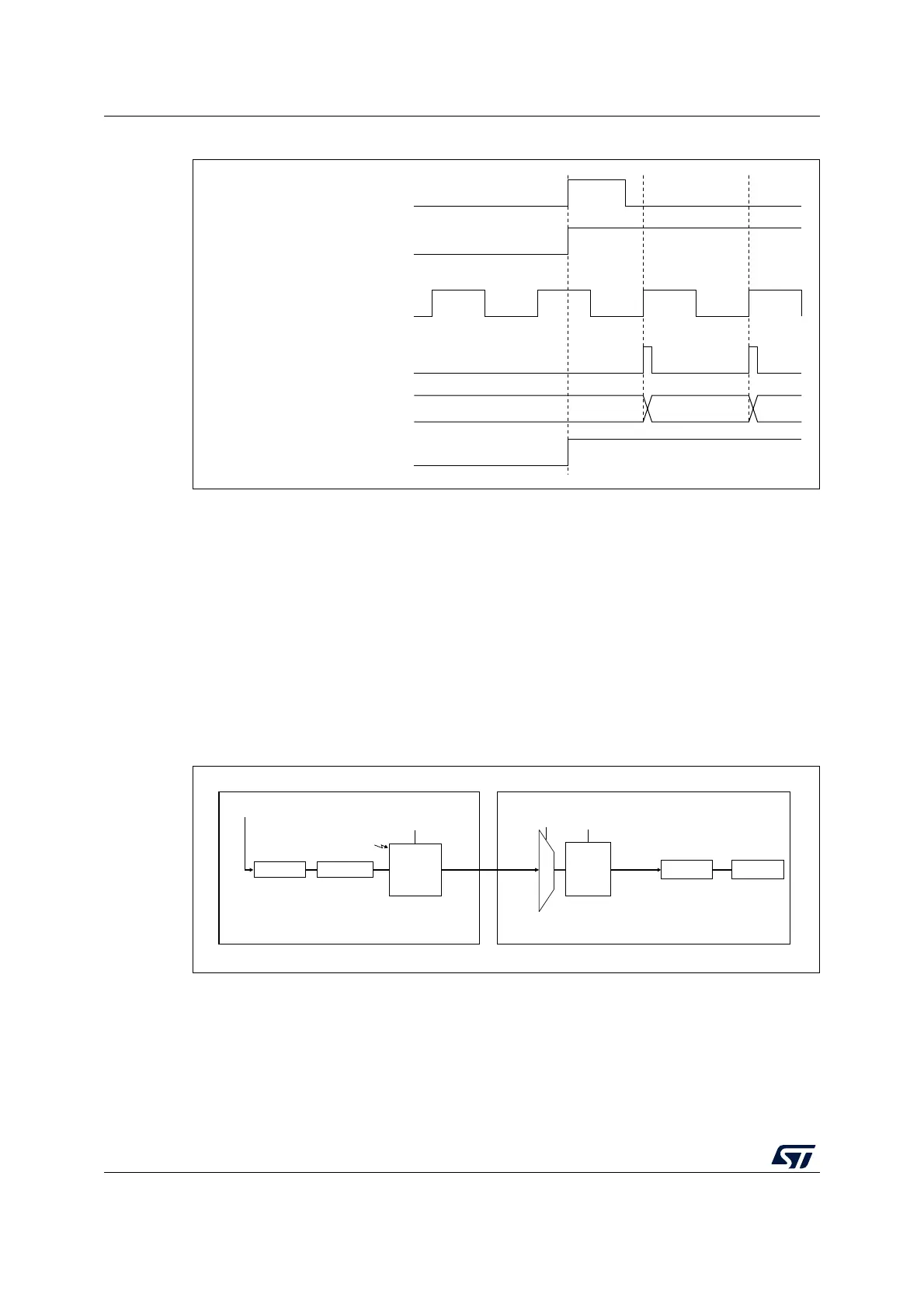

Figure 152. Control circuit in external clock mode 2 + trigger mode

14.3.15 Timer synchronization

The TIMx timers are linked together internally for timer synchronization or chaining. When

one Timer is configured in Master mode, it can reset, start, stop or clock the counter of

another Timer configured in Slave mode.

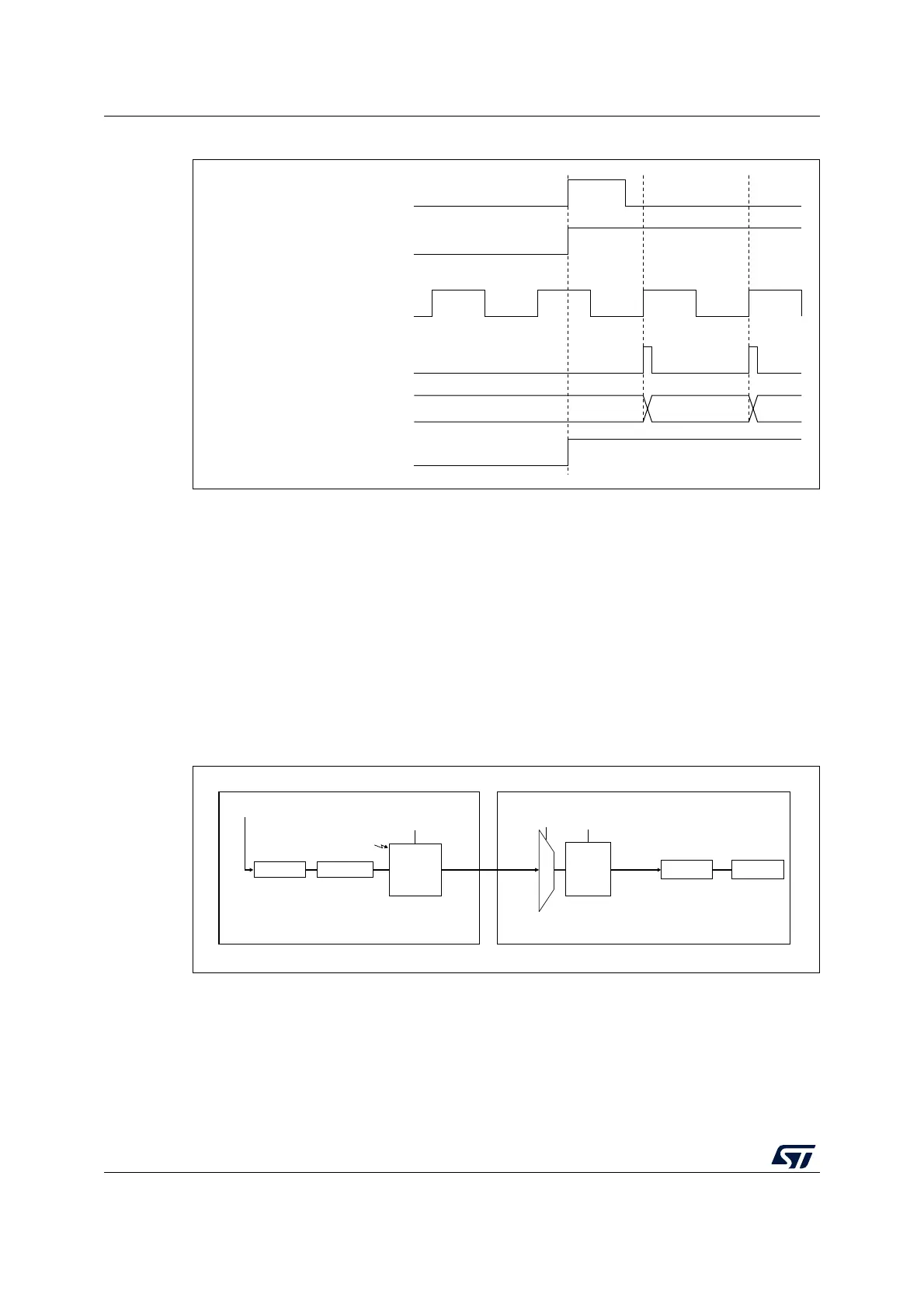

Figure 153 presents an overview of the trigger selection and the master mode selection

blocks.

Note: The clock of the slave timer must be enabled prior to receiving events from the master timer,

and must not be changed on-the-fly while triggers are received from the master timer.

Using one timer as prescaler for another timer

Figure 153. Master/Slave timer example

MS33110V1

34 35 36

TIF

Counter register

Counter clock = CK_CNT = CK_PSC

ETR

CEN/CNT_EN

TI1

MS37387V1

Counter

Master

mode

control

UEV

Prescaler

Clock

CounterPrescaler

CK_PSCTRGO1

MMS SMS

TS

Input trigger

selection

TIM1 TIM2

Slave

mode

control

ITR0

Loading...

Loading...