Serial peripheral interface (SPI) RM0033

698/1381 RM0033 Rev 9

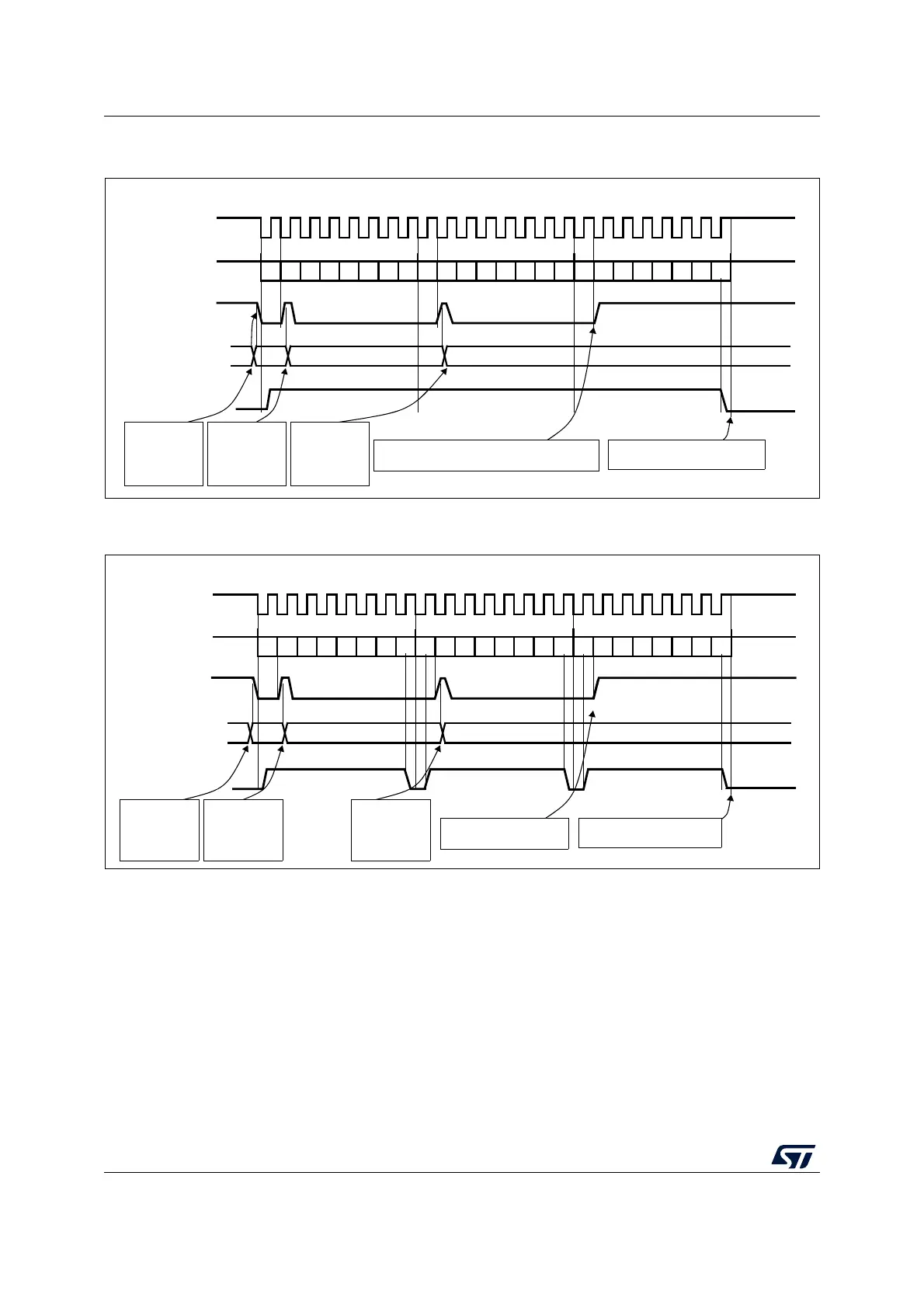

Figure 257. TXE/BSY behavior in Master transmit-only mode (BIDIMODE=0 and RXONLY=0)

in case of continuous transfers

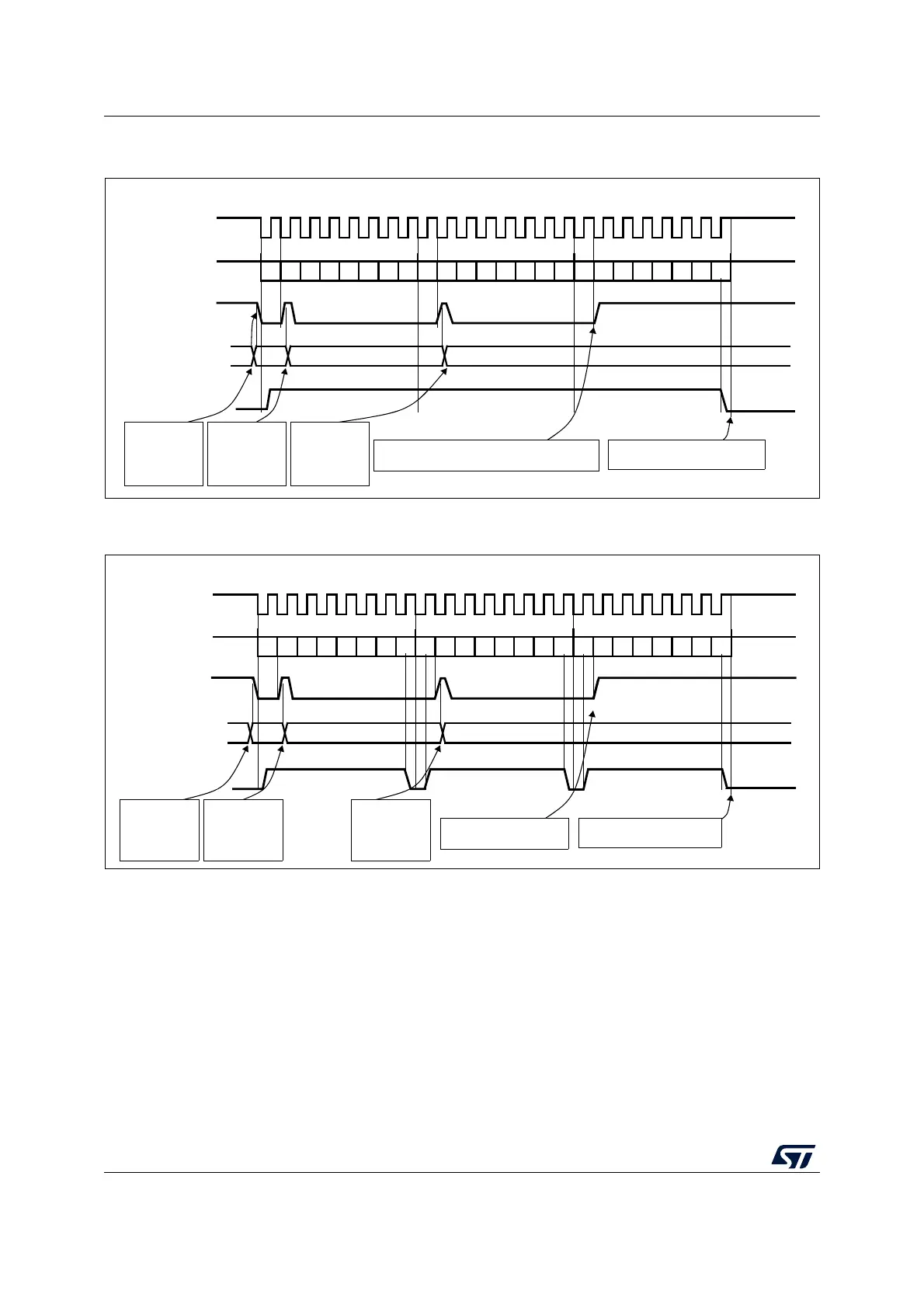

Figure 258. TXE/BSY in Slave transmit-only mode (BIDIMODE=0 and RXONLY=0) in case of

continuous transfers

Bidirectional transmit procedure (BIDIMODE=1 and BIDIOE=1)

In this mode, the procedure is similar to the procedure in Transmit-only mode except that

the BIDIMODE and BIDIOE bits both have to be set in the SPI_CR2 register before enabling

the SPI.

Unidirectional receive-only procedure (BIDIMODE=0 and RXONLY=1)

In this mode, the procedure can be reduced as described below (see Figure 259):

0xF1

Tx buffer

TXE flag

0xF2

BSY flag

0xF3

software writes

0xF1 into

SPI_DR

software waits

until TXE=1 and

writes 0xF2 into

SPI_DR

set by hardware

cleared by software

set by hardware

cleared by software

set by hardware

set by hardware

SCK

reset by hardware

Example in Master mode with CPOL=1, CPHA=1

(write to SPI_DR)

MISO/MOSI (out)

DATA 1 = 0xF1

DATA 2 = 0xF2

DATA 3 = 0xF3

software waits

until TXE=1 and

writes 0xF3 into

SPI_DR

software waits until BSY=0software waits until TXE=1

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

b0 b1 b2 b3 b4 b5 b6 b7

ai17345

0xF1

Tx buffer

TXE flag

0xF2

BSY flag

0xF3

software writes

0xF1 into

SPI_DR

software waits

until TXE=1 and

writes 0xF2 into

SPI_DR

set by hardware

cleared by software

set by hardware

cleared by software

set by hardware

set by hardware

SCK

reset by hardware

Example in slave mode with CPOL=1, CPHA=1

(write to SPI_DR)

MISO/MOSI (out)

DATA 1 = 0xF1 DATA 2 = 0xF2

DATA 3 = 0xF3

software waits

until TXE=1 and

writes 0xF3 into

SPI_DR

software waits until BSY=0software waits until TXE=1

b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7 b0 b1 b2 b3 b4 b5 b6 b7

ai17346

Loading...

Loading...