Random number generator (RNG) RM0033

544/1381 RM0033 Rev 9

20 Random number generator (RNG)

This section applies to the whole STM32F20x and STM32F21x family, unless otherwise

specified.

20.1 RNG introduction

The RNG processor is a random number generator, based on a continuous analog noise,

that provides a random 32-bit value to the host when read.

The RNG passed the FIPS PUB 140-2 (2001 October 10) tests with a success ratio of 99%.

20.2 RNG main features

• It delivers 32-bit random numbers, produced by an analog generator

• 40 periods of the RNG_CLK clock signal between two consecutive random numbers

• Monitoring of the RNG entropy to flag abnormal behavior (generation of stable values,

or of a stable sequence of values)

• It can be disabled to reduce power consumption

20.3 RNG functional description

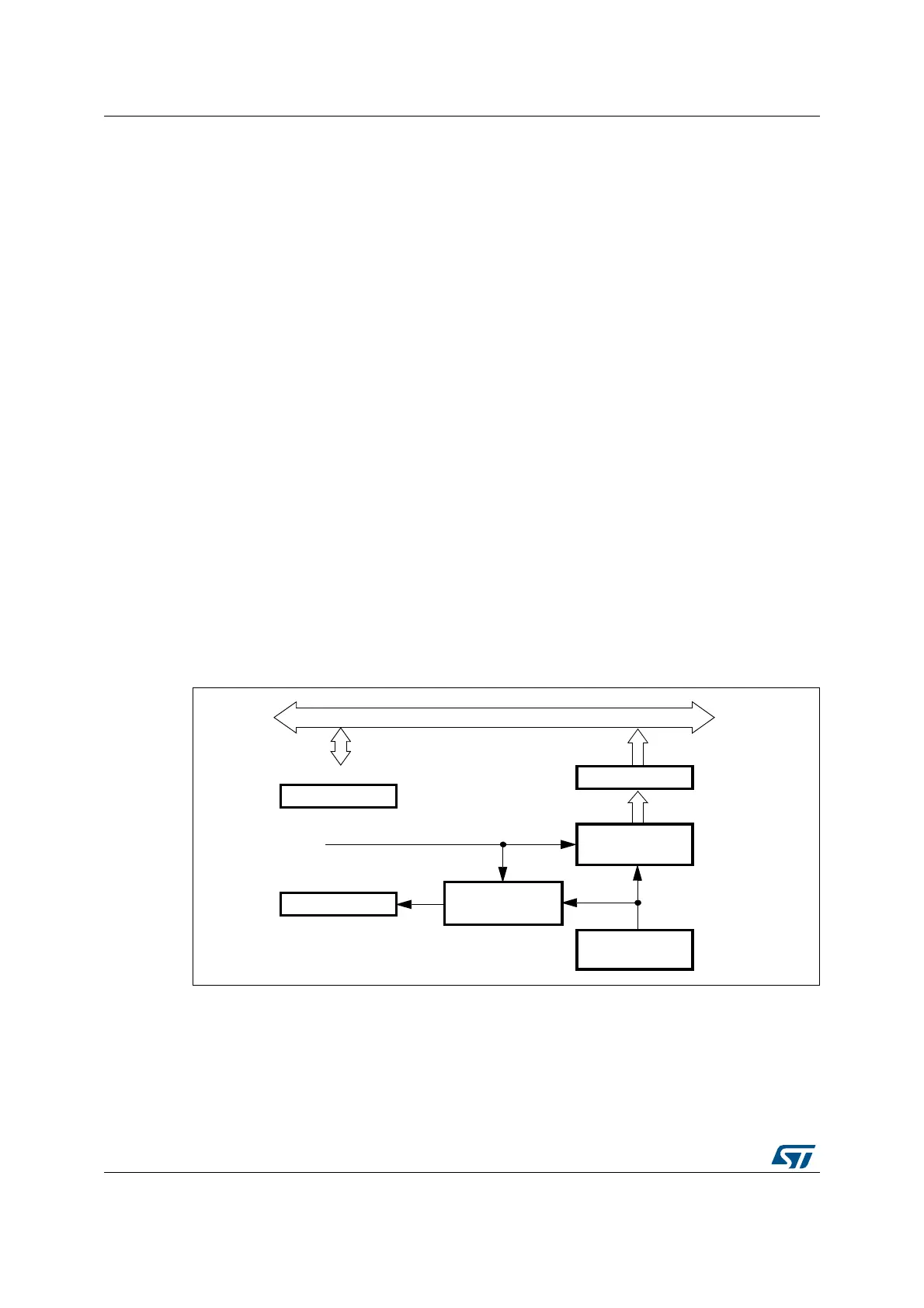

Figure 210 shows the RNG block diagram.

Figure 210. Block diagram

1. For more details about RNG Clock (RNG_CLK) source, please refer to Section 5: Reset and clock control

(RCC).

The random number generator implements an analog circuit. This circuit generates seeds

that feed a linear feedback shift register (RNG_LFSR) in order to produce 32-bit random

numbers.

32-bit AHB bus

RNG_DR

RNG

_CR

RNG

_SR

Status register

Control register

fault detector

LFSR

Analog seed

RNG_CLK

Clock checker &

data register

Shift Register

feed a Linear Feedback

ai16080

Loading...

Loading...