RM0033 Rev 9 459/1381

RM0033 General-purpose timers (TIM9 to TIM14)

483

15.4 TIM9 and TIM12 registers

Refer to Section 2.2 for a list of abbreviations used in register descriptions.

The peripheral registers have to be written by half-words (16 bits) or words (32 bits). Read

accesses can be done by bytes (8 bits), half-words (16 bits) or words (32 bits).

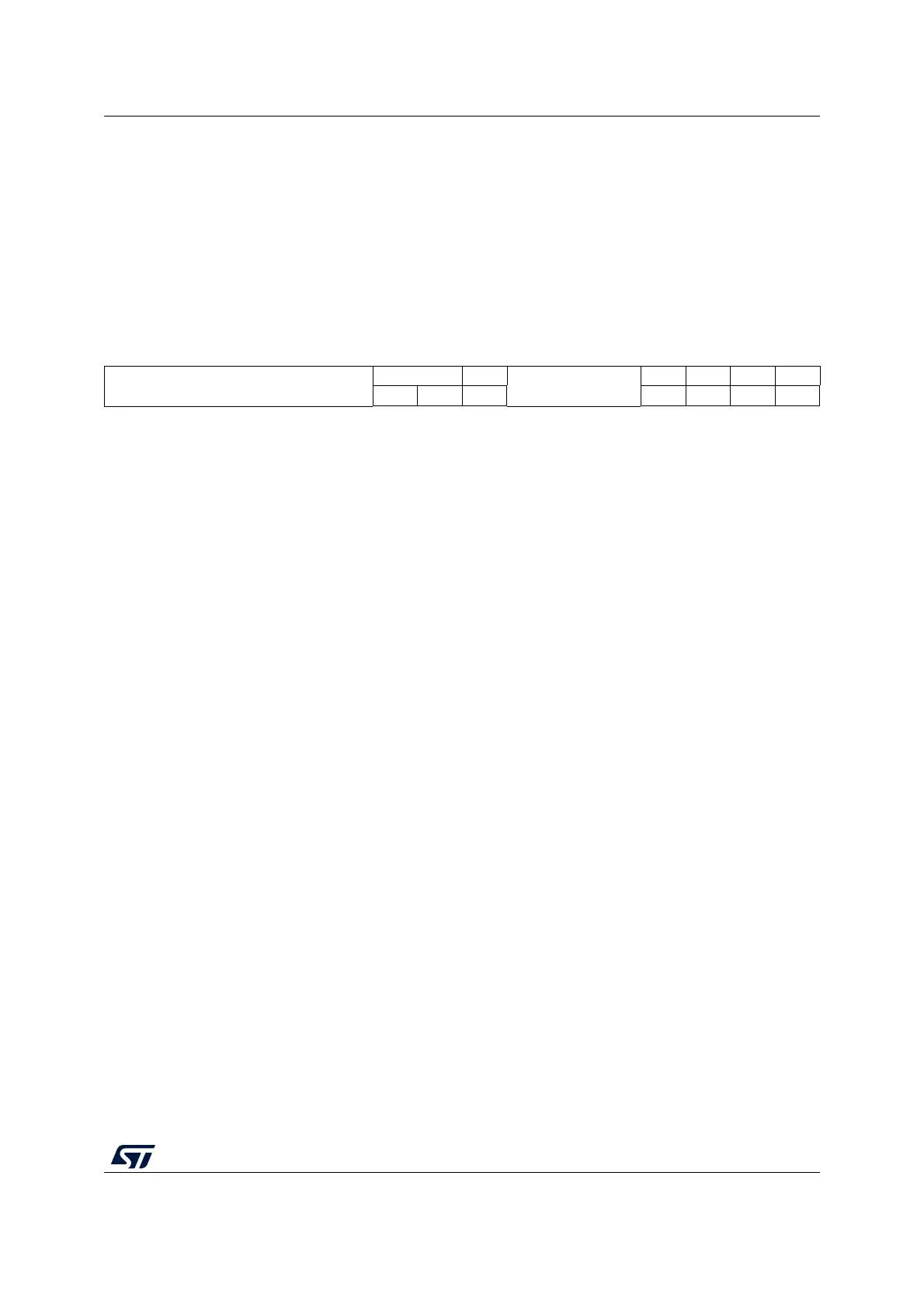

15.4.1 TIM9/12 control register 1 (TIMx_CR1)

Address offset: 0x00

Reset value: 0x0000

1514131211109876543210

Reserved

CKD[1:0] ARPE

Reserved

OPM URS UDIS CEN

rw rw rw rw rw rw rw

Bits 15:10 Reserved, must be kept at reset value.

Bits 9:8 CKD: Clock division

This bit-field indicates the division ratio between the timer clock (CK_INT) frequency and

sampling clock used by the digital filters (TIx),

00: t

DTS

= t

CK_INT

01: t

DTS

= 2 × t

CK_INT

10: t

DTS

= 4 × t

CK_INT

11: Reserved

Bit 7 ARPE: Auto-reload preload enable

0: TIMx_ARR register is not buffered.

1: TIMx_ARR register is buffered.

Bits 6:4 Reserved, must be kept at reset value.

Bit 3 OPM: One-pulse mode

0: Counter is not stopped on the update event

1: Counter stops counting on the next update event (clearing the CEN bit).

Bit 2 URS: Update request source

This bit is set and cleared by software to select the UEV event sources.

0: Any of the following events generates an update interrupt if enabled:

– Counter overflow

– Setting the UG bit

1: Only counter overflow generates an update interrupt if enabled.

Bit 1 UDIS: Update disable

This bit is set and cleared by software to enable/disable update event (UEV) generation.

0: UEV enabled. An UEV is generated by one of the following events:

– Counter overflow

– Setting the UG bit

Buffered registers are then loaded with their preload values.

1: UEV disabled. No UEV is generated, shadow registers keep their value (ARR, PSC,

CCRx). The counter and the prescaler are reinitialized if the UG bit is set.

Bit 0 CEN: Counter enable

0: Counter disabled

1: Counter enabled

CEN is cleared automatically in one-pulse mode, when an update event occurs.

Loading...

Loading...