Hash processor (HASH) RM0033

558/1381 RM0033 Rev 9

Procedure where the data are loaded by DMA

In this case it is not possible to predict if a DMA transfer is in progress or if the process is

ongoing. Thus, you must stop the DMA transfers, then wait until the HASH is ready in order

to interrupt the processing of a message.

• Interrupting a processing:

– Clear the DMAE bit to disable the DMA interface

– Wait until the current DMA transfer is complete (wait for DMAES = 0 in the

HASH_SR register). Note that the block may or not have been totally transferred

to the HASH.

– Disable the corresponding channel in the DMA controller

– Wait until the hash processor is ready (no block is being processed), that is wait

for DINIS = 1

• The context saving and context restoring phases are the same as above (see

Procedure where the data are loaded by software).

Reconfigure the DMA controller so that it transfers the end of the message. You can now

restart the processing from the point where it was interrupted by setting the DMAE bit.

Note: If context swapping does not involve HMAC operations, the HASH_CSR38 to

HASH_CSR50 registers do not have to be saved and restored.

If context swapping occurs between two blocks (the last block was completely processed

and the next block has not yet been pushed into the IN FIFO, NBW = 000 in the HASH_CR

register), the HASH_CSR22 to HASH_CSR37 registers do not have to be saved and

restored.

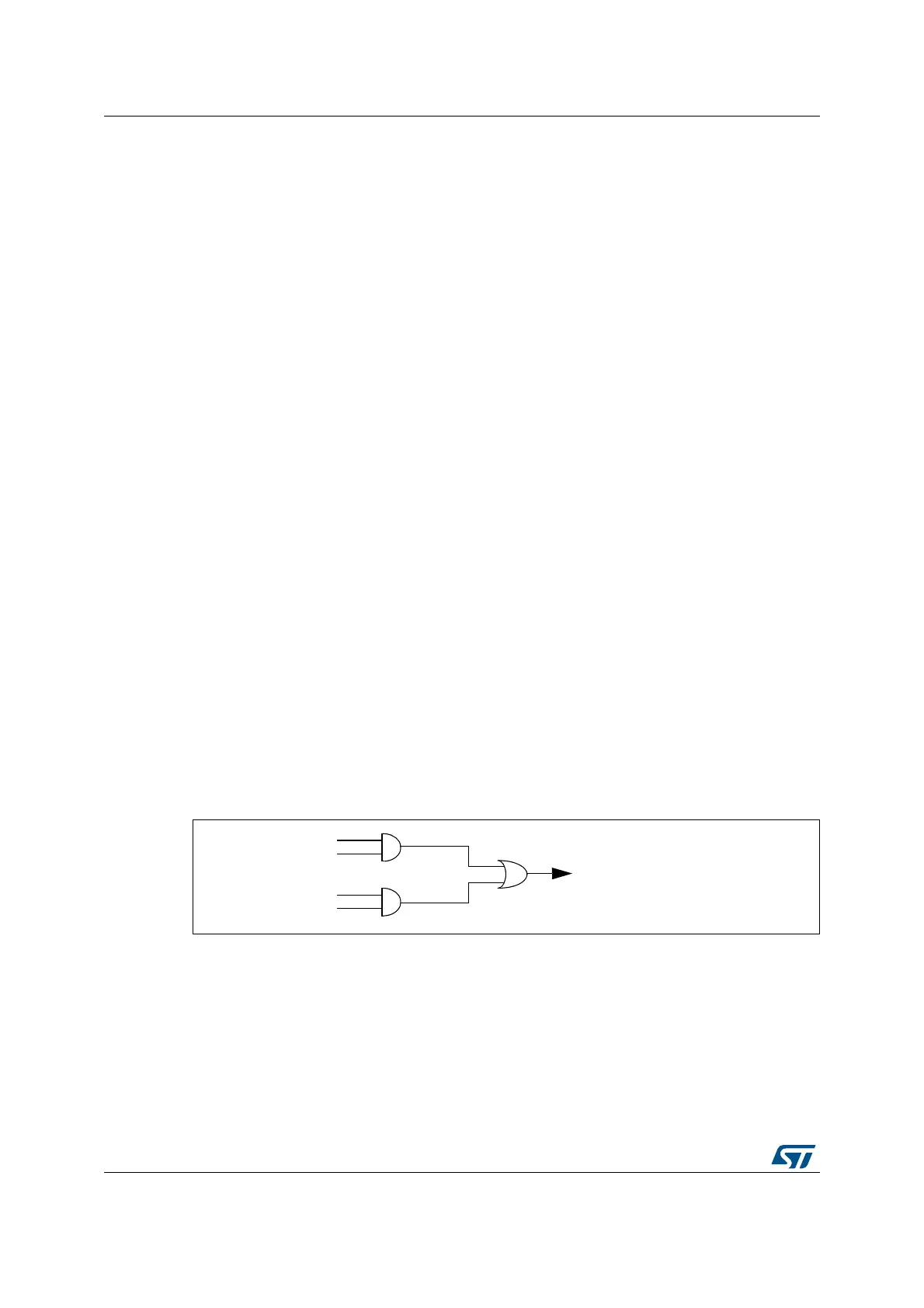

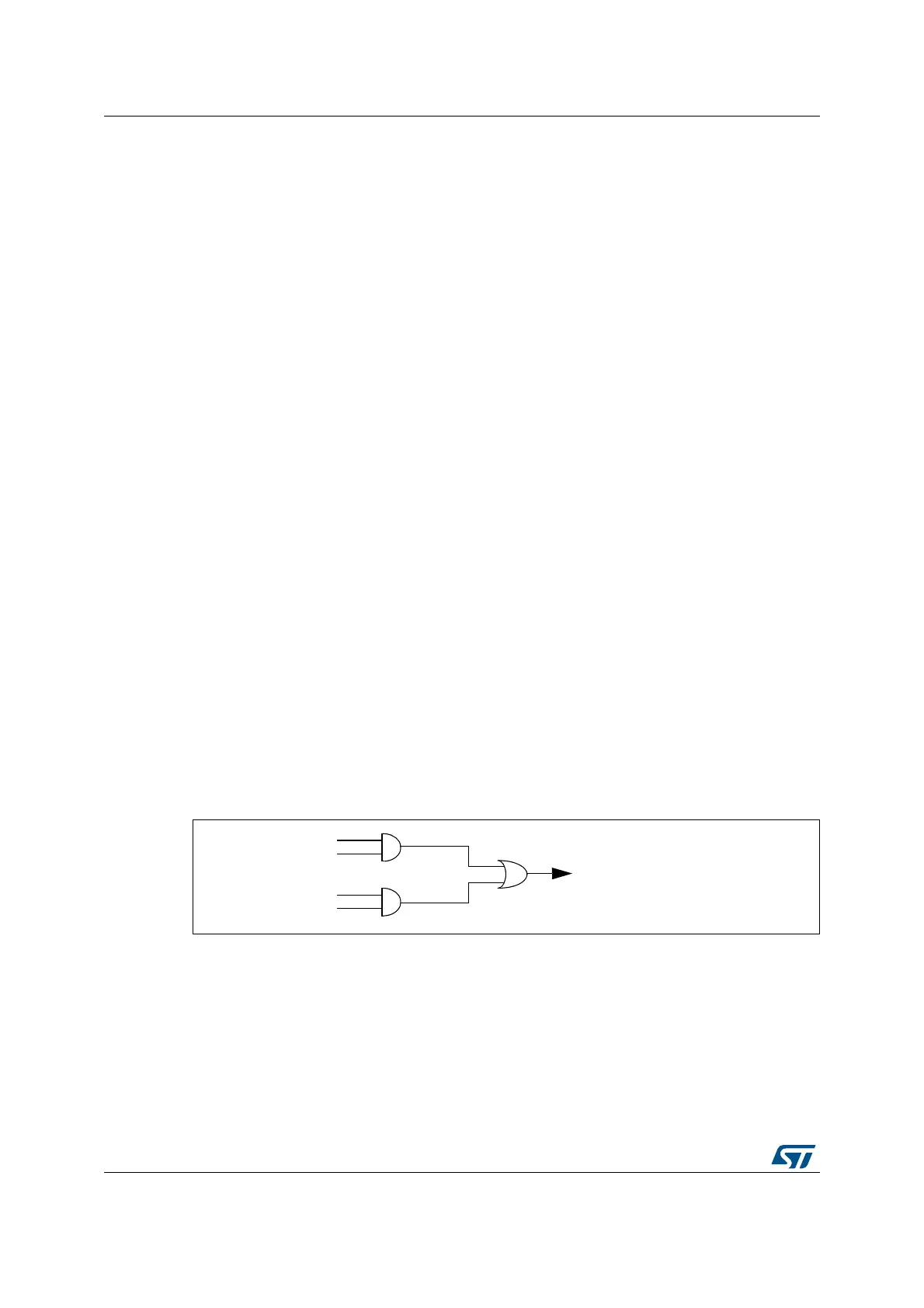

21.3.8 HASH interrupt

There are two individual maskable interrupt sources generated by the HASH processor.

They are connected to the same interrupt vector.

You can enable or disable the interrupt sources individually by changing the mask bits in the

HASH_IMR register. Setting the appropriate mask bit to 1 enables the interrupt.

The status of the individual interrupt sources can be read from the HASH_SR register.

Figure 214. HASH interrupt mapping diagram

DCIS

DCIM

DINIS

DINIM

HASH interrupt to NVIC

ai16086

Loading...

Loading...