RM0033 Rev 9 659/1381

RM0033 Universal synchronous asynchronous receiver transmitter (USART)

681

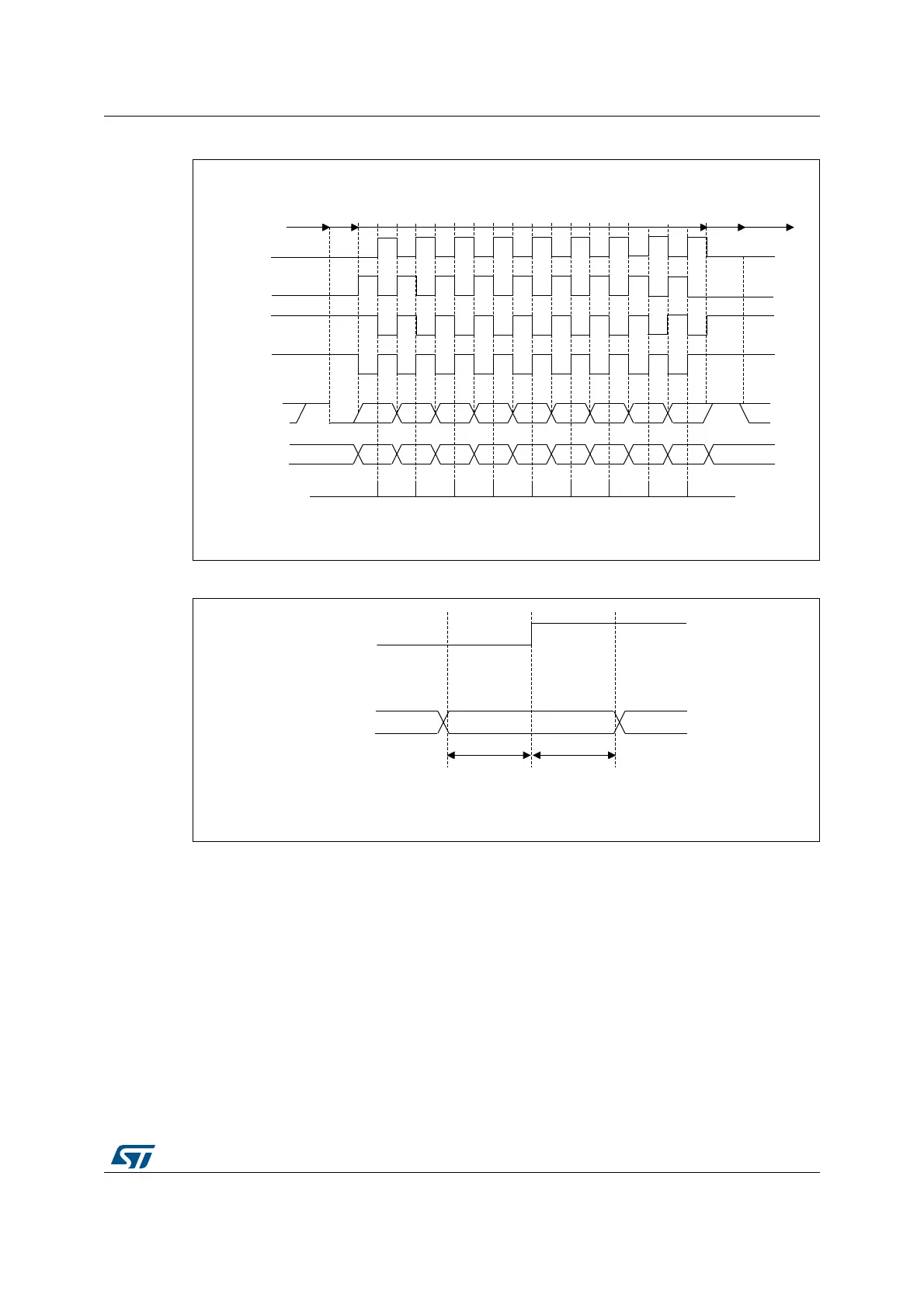

Figure 236. USART data clock timing diagram (M=1)

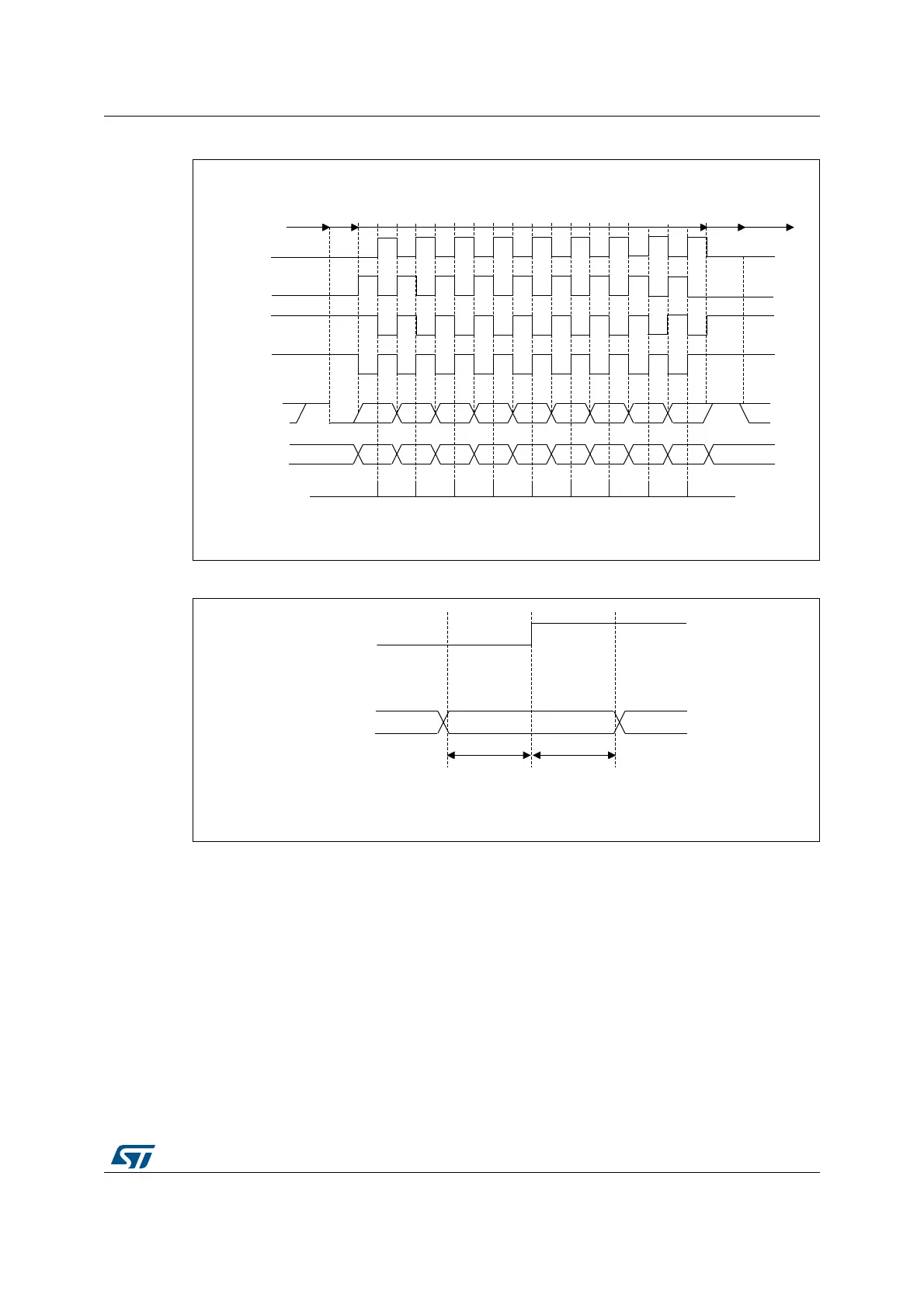

Figure 237. RX data setup/hold time

Note: The function of CK is different in Smartcard mode. Refer to the Smartcard mode chapter for

more details.

24.3.10 Single-wire half-duplex communication

The single-wire half-duplex mode is selected by setting the HDSEL bit in the USART_CR3

register. In this mode, the following bits must be kept cleared:

• LINEN and CLKEN bits in the USART_CR2 register,

• SCEN and IREN bits in the USART_CR3 register.

The USART can be configured to follow a single-wire half-duplex protocol where the TX and

RX lines are internally connected. The selection between half- and full-duplex

communication is made with a control bit ‘HALF DUPLEX SEL’ (HDSEL in USART_CR3).

MSv31160V1

0 1 2 3 4 5 6 8

0 1 2 3 4 5 6 8

*

*

*

*

MSB

MSB

LSB

LSBStart

Start Stop

Idle or

preceding

transmission

Idle or next

transmission

*

*LBCL bit controls last data pulse

Capture

strobe

Data on RX

(from slave)

Data on TX

(from master)

Clock (CPOL=1,

CPHA=1

Clock (CPOL=1,

CPHA=0

Clock (CPOL=0,

CPHA=1

Clock (CPOL=0,

CPHA=0

Stop

M=1 (9 data bits)

7

7

MSv31161V2

Data on RX (from slave)

CK

(capture strobe on CK rising

edge in this example)

Valid DATA bit

t

SETUP

t

HOLD

t

SETUP=

t

HOLD

1/16 bit time

Loading...

Loading...