General-purpose timers (TIM2 to TIM5) RM0033

384/1381 RM0033 Rev 9

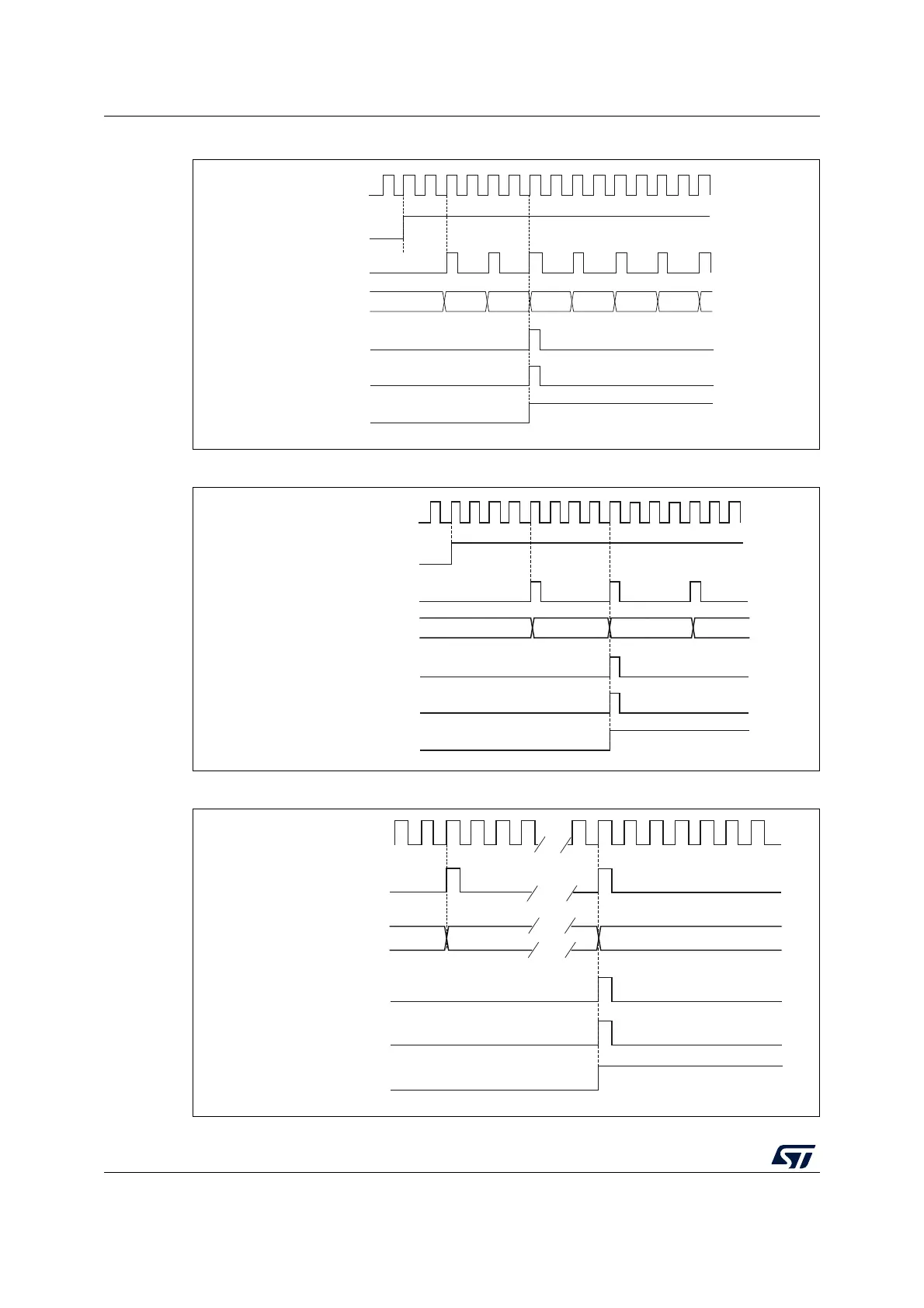

Figure 123. Counter timing diagram, internal clock divided by 2

Figure 124. Counter timing diagram, internal clock divided by 4

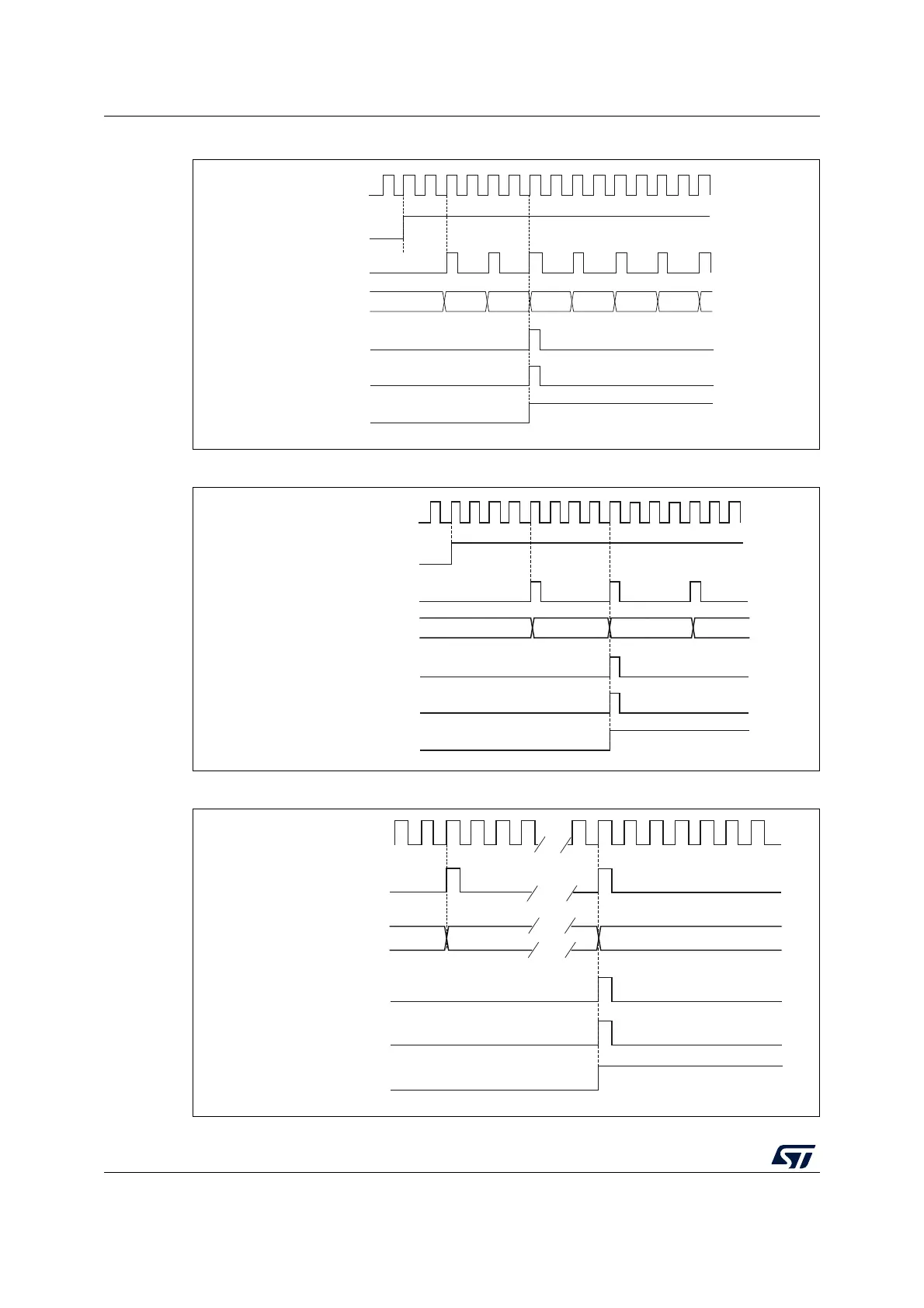

Figure 125. Counter timing diagram, internal clock divided by N

MSv37306V1

CK_INT

CNT_EN

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter underflow

Update interrupt flag (UIF)

0002 0001 0000 0036 0035 0034 0033

MS40511V1

0036

00350001 0000

CK_INT

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter underflow

Update interrupt flag (UIF)

CNT_EN

MS37340V1

001F20

CK_INT

Timerclock = CK_CNT

Counter register

Update event (UEV)

Counter overflow

Update interrupt flag (UIF)

36

Loading...

Loading...