RM0033 Rev 9 673/1381

RM0033 Universal synchronous asynchronous receiver transmitter (USART)

681

24.6.2 Data register (USART_DR)

Address offset: 0x04

Reset value: 0xXXXX XXXX

24.6.3 Baud rate register (USART_BRR)

Note: The baud counters stop counting if the TE or RE bits are disabled respectively.

Address offset: 0x08

Reset value: 0x0000 0000

24.6.4 Control register 1 (USART_CR1)

Address offset: 0x0C

Reset value: 0x0000 0000

Bits 31:9 Reserved, must be kept at reset value

Bits 8:0 DR[8:0]: Data value

Contains the Received or Transmitted data character, depending on whether it is read from

or written to.

The Data register performs a double function (read and write) since it is composed of two

registers, one for transmission (TDR) and one for reception (RDR)

The TDR register provides the parallel interface between the internal bus and the output shift

register (see Figure 1).

The RDR register provides the parallel interface between the input shift register and the

internal bus.

When transmitting with the parity enabled (PCE bit set to 1 in the USART_CR1 register), the

value written in the MSB (bit 7 or bit 8 depending on the data length) has no effect because

it is replaced by the parity.

When receiving with the parity enabled, the value read in the MSB bit is the received parity

bit.

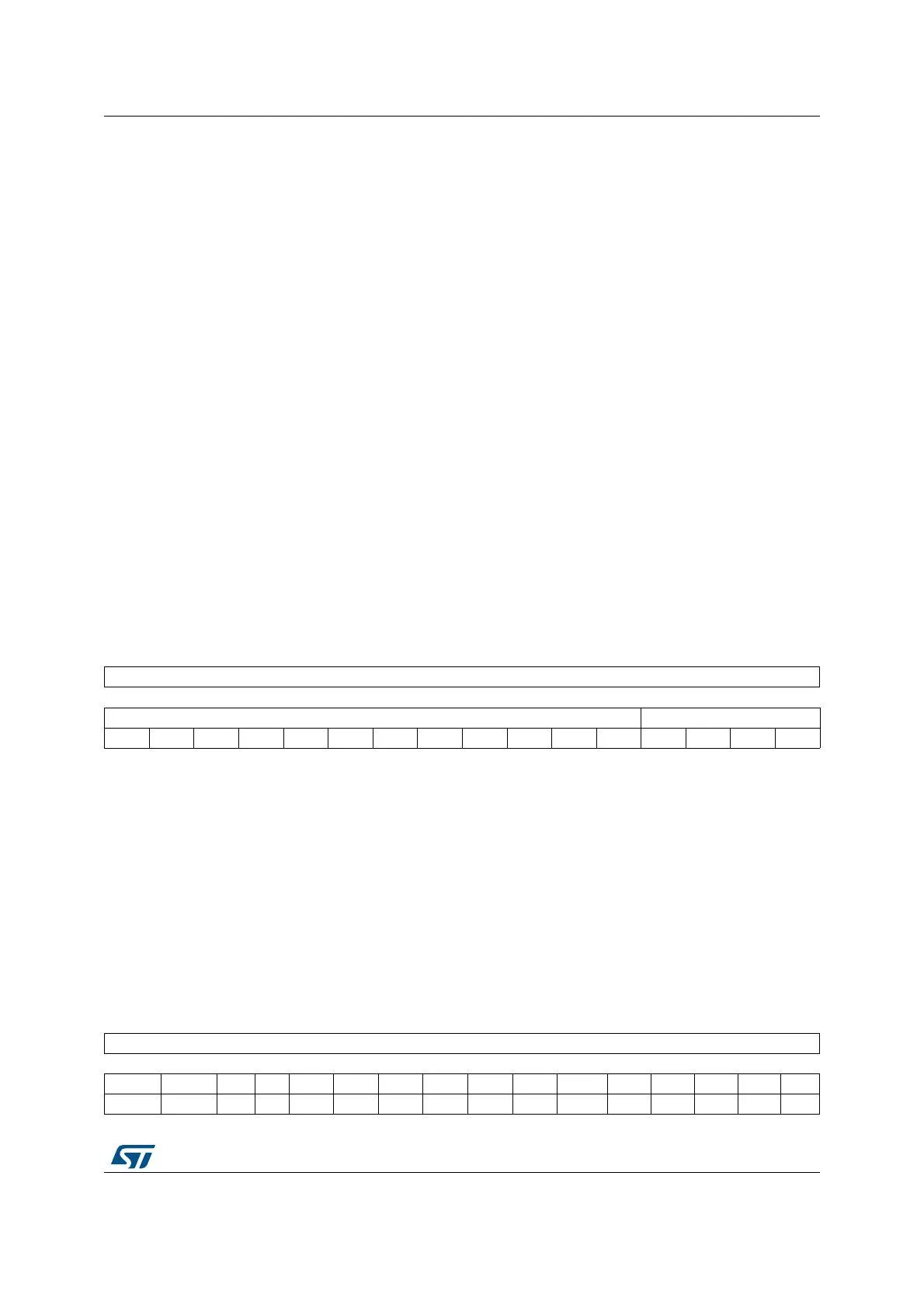

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DIV_Mantissa[11:0] DIV_Fraction[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value

Bits 15:4 DIV_Mantissa[11:0]: mantissa of USARTDIV

These 12 bits define the mantissa of the USART Divider (USARTDIV)

Bits 3:0 DIV_Fraction[3:0]: fraction of USARTDIV

These 4 bits define the fraction of the USART Divider (USARTDIV). When OVER8=1, the

DIV_Fraction3 bit is not considered and must be kept cleared.

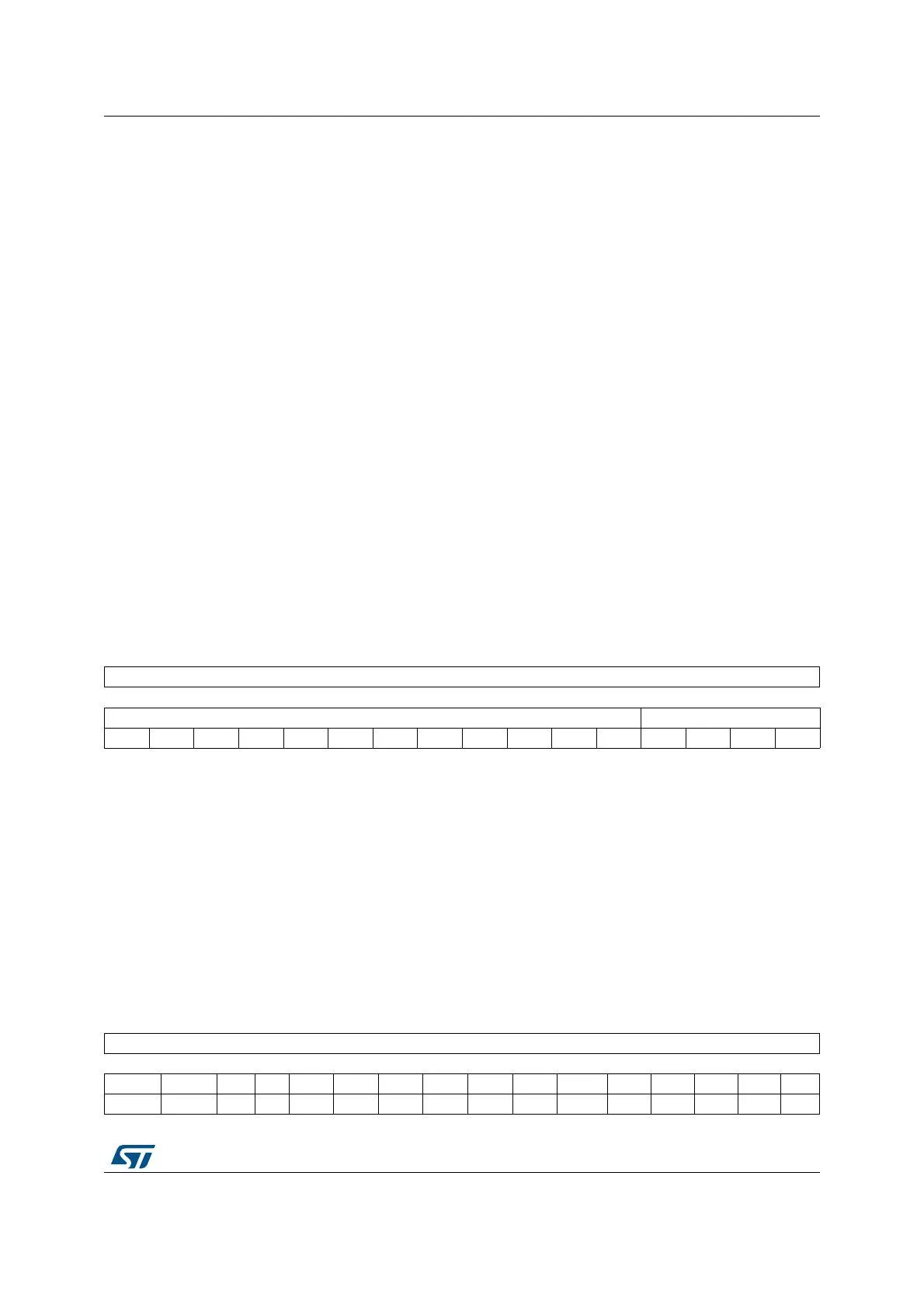

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OVER8 Reserved UE M WAKE PCE PS PEIE TXEIE TCIE RXNEIE IDLEIE TE RE RWU SBK

rw Res. rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...