RM0033 Rev 9 1343/1381

RM0033 Debug support (DBG)

1349

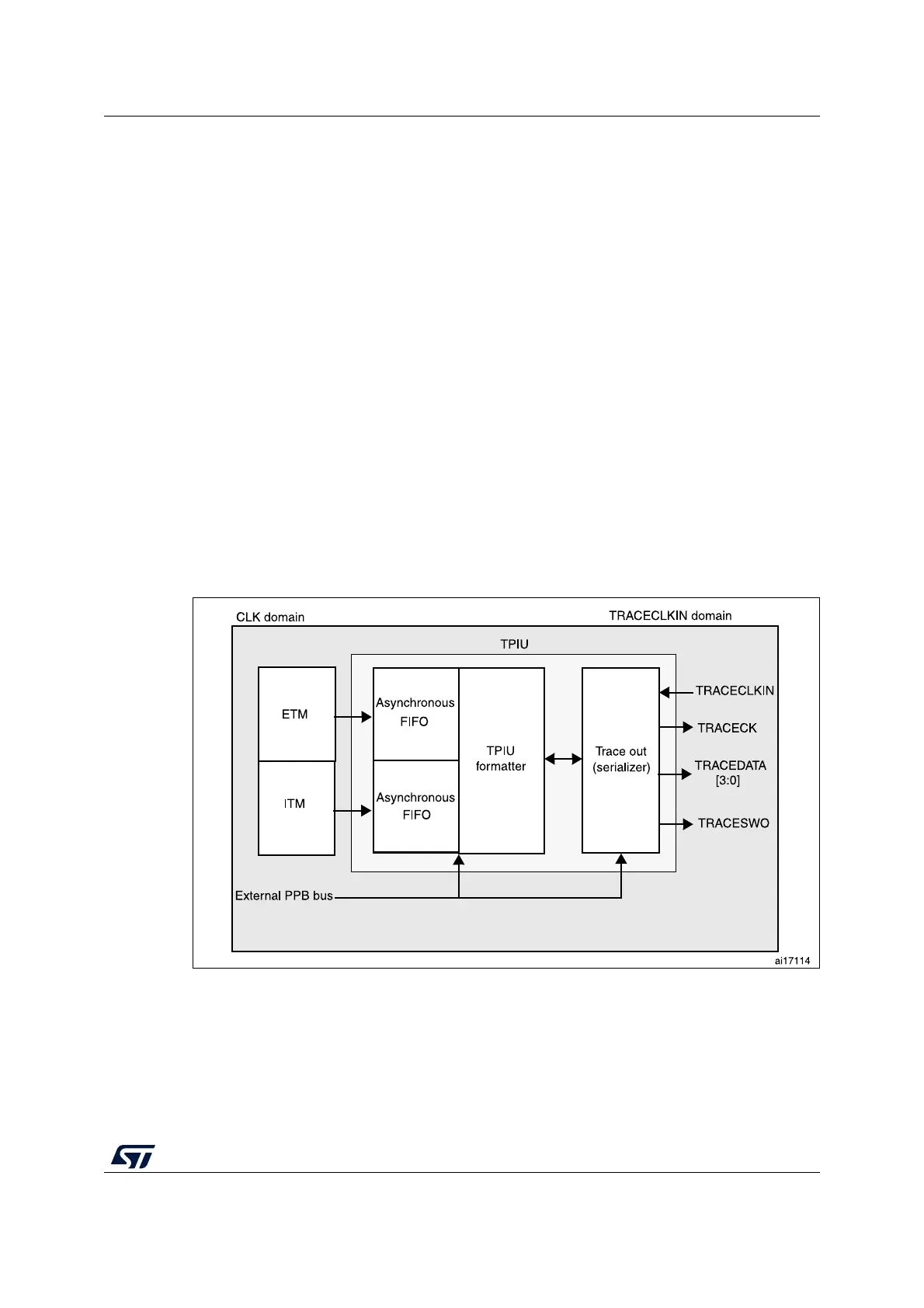

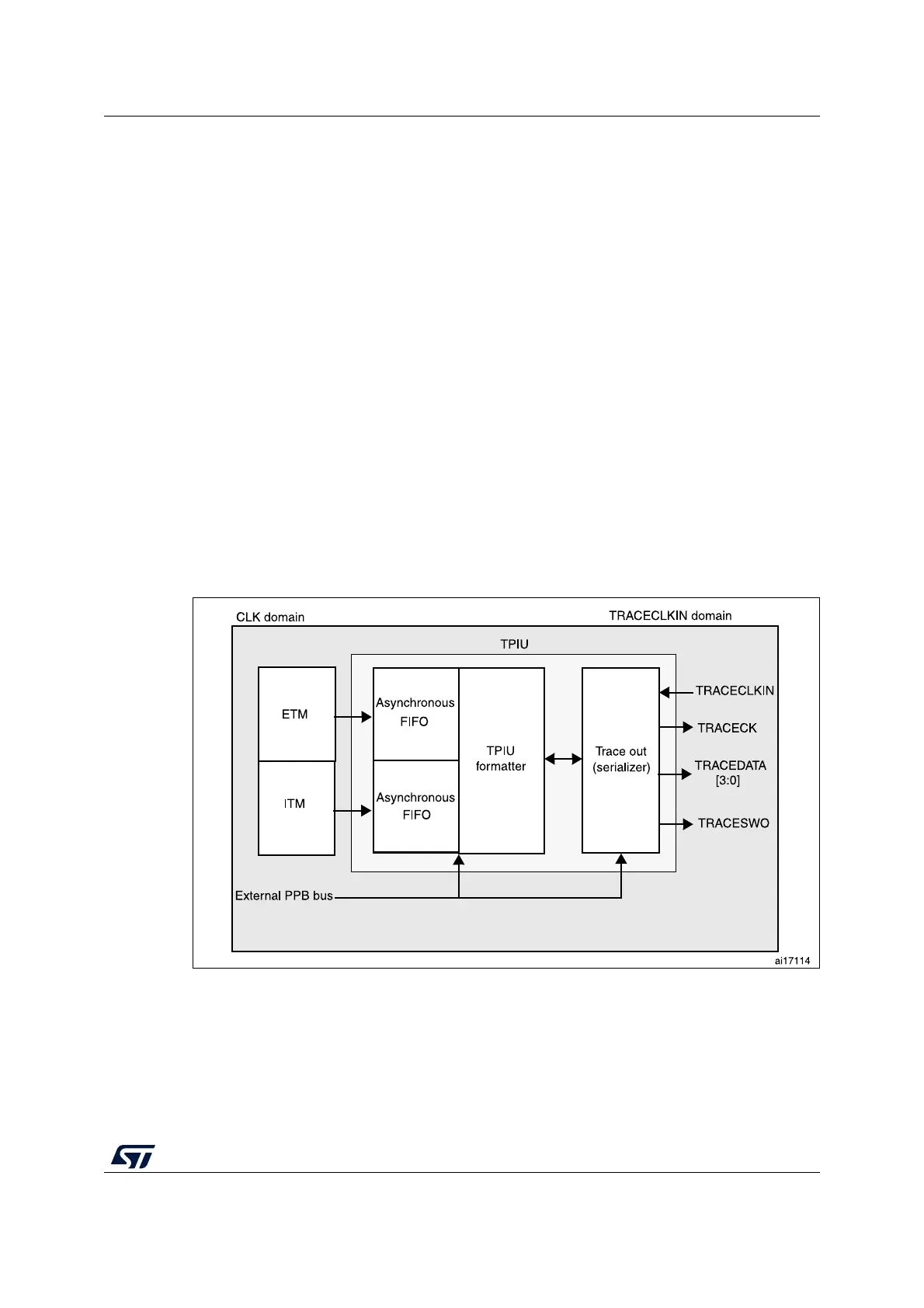

32.17 TPIU (trace port interface unit)

32.17.1 Introduction

The TPIU acts as a bridge between the on-chip trace data from the ITM and the ETM.

The output data stream encapsulates the trace source ID, that is then captured by a trace

port analyzer (TPA).

The core embeds a simple TPIU, especially designed for low-cost debug (consisting of a

special version of the CoreSight TPIU).

Figure 422. TPIU block diagram

Bits 15: Reserved, must be kept at reset value.

Bit 1 DBG_TIM8_STOP: TIM8 counter stopped when core is halted

0: The clock of the involved timer counter is fed even if the core is halted

1: The clock of the involved timer counter is stopped and the outputs are disabled when the

core is halted

Bit 0 DBG_TIM1_STOP: TIM1 counter stopped when core is halted

0: The clock of the involved timer counter is fed even if the core is halted

1: The clock of the involved timer counter is stopped and the outputs are disabled when the

core is halted

Loading...

Loading...