RM0033 Rev 9 637/1381

RM0033 Universal synchronous asynchronous receiver transmitter (USART)

681

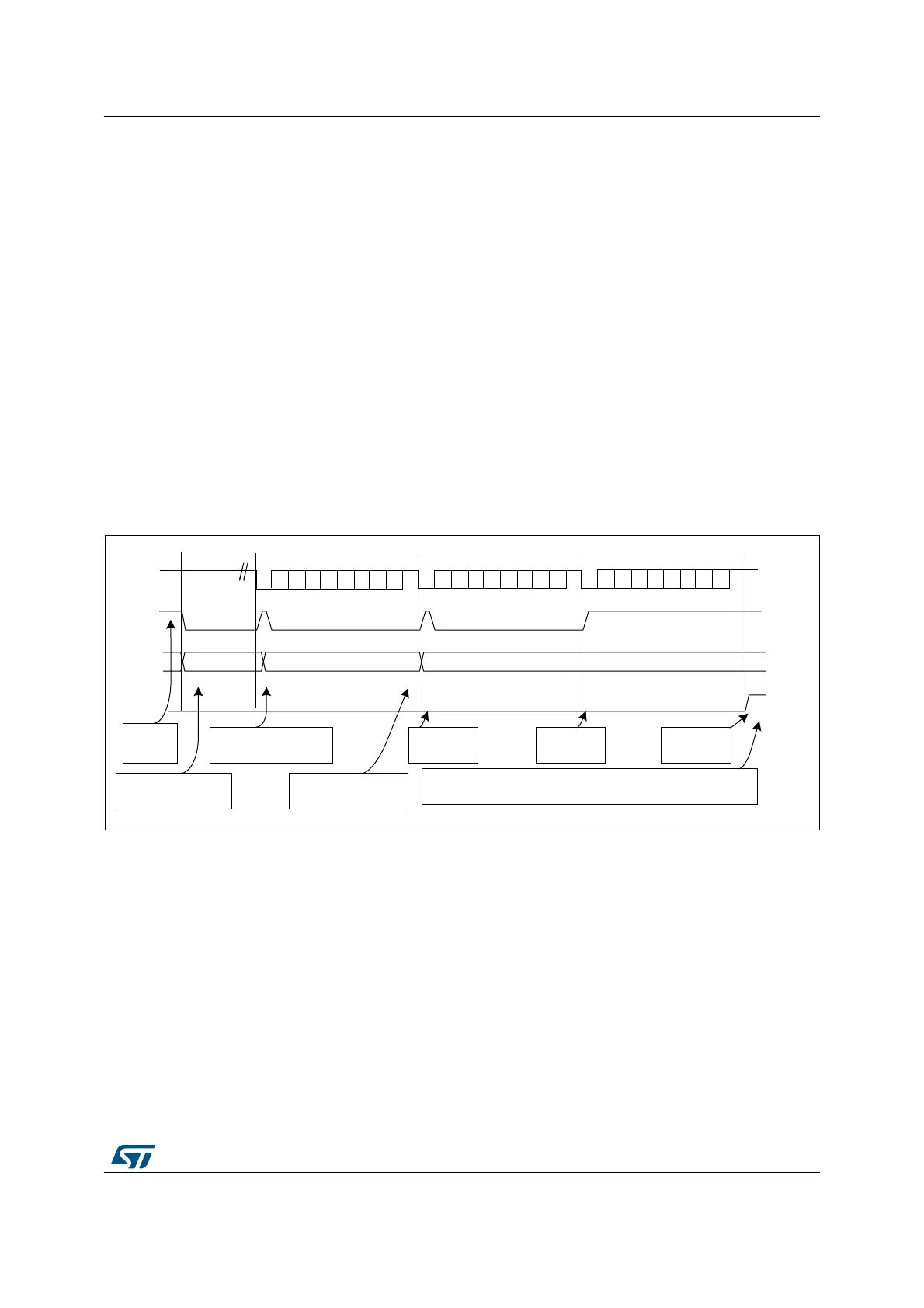

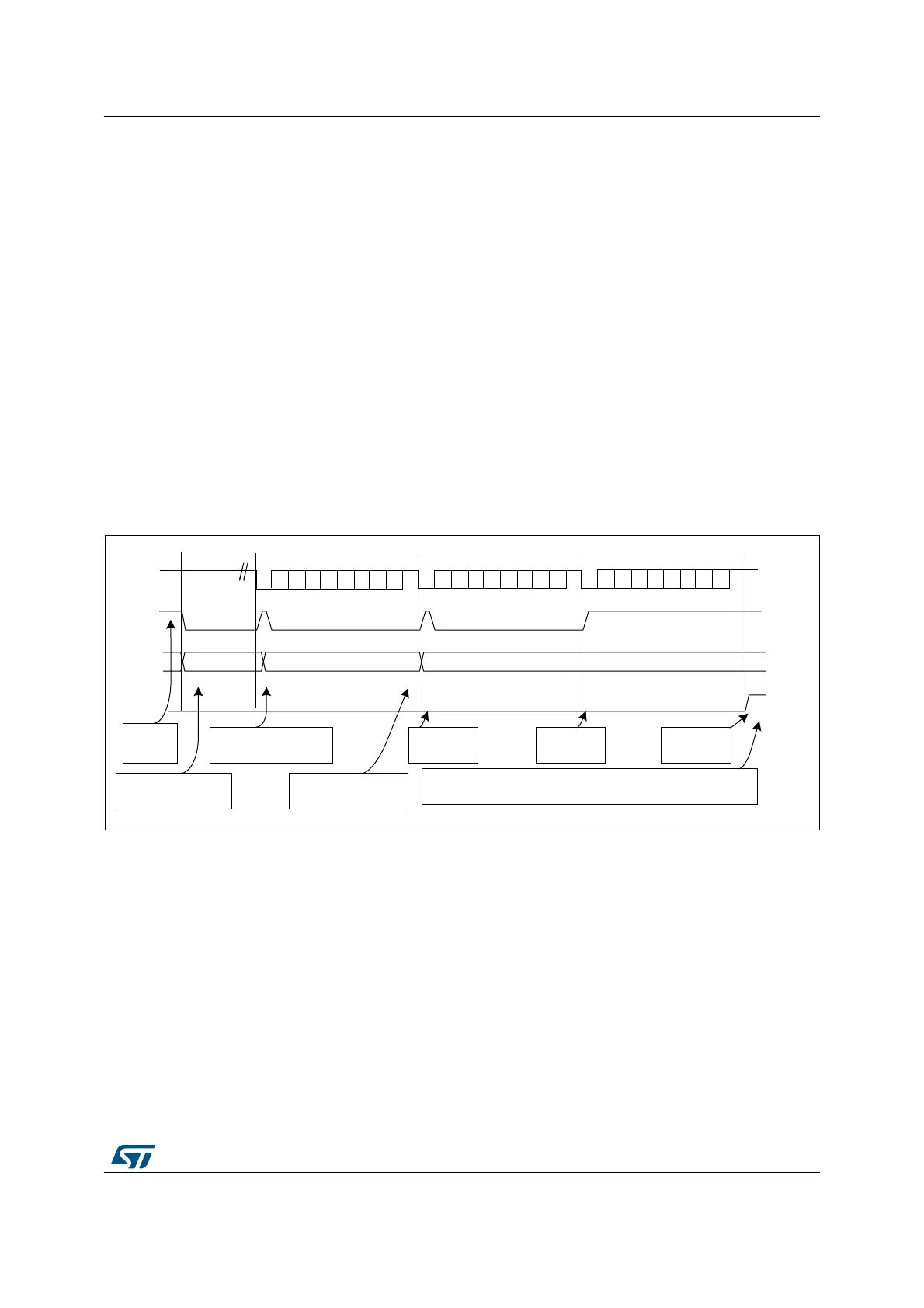

When a transmission is taking place, a write instruction to the USART_DR register stores

the data in the TDR register and which is copied in the shift register at the end of the current

transmission.

When no transmission is taking place, a write instruction to the USART_DR register places

the data directly in the shift register, the data transmission starts, and the TXE bit is

immediately set.

If a frame is transmitted (after the stop bit) and the TXE bit is set, the TC bit goes high. An

interrupt is generated if the TCIE bit is set in the USART_CR1 register.

After writing the last data into the USART_DR register, it is mandatory to wait for TC=1

before disabling the USART or causing the microcontroller to enter the low-power mode

(see

Figure 226: TC/TXE behavior when transmitting).

The TC bit is cleared by the following software sequence:

1. A read from the USART_SR register

2. A write to the USART_DR register

Note: The TC bit can also be cleared by writing a ‘0 to it. This clearing sequence is recommended

only for Multibuffer communication.

Figure 226. TC/TXE behavior when transmitting

Break characters

Setting the SBK bit transmits a break character. The break frame length depends on the M

bit (see

Figure 224).

If the SBK bit is set to ‘1 a break character is sent on the TX line after completing the current

character transmission. This bit is reset by hardware when the break character is completed

(during the stop bit of the break character). The USART inserts a logic 1 bit at the end of the

last break frame to guarantee the recognition of the start bit of the next frame.

Note: If the software resets the SBK bit before the commencement of break transmission, the

break character will not be transmitted. For two consecutive breaks, the SBK bit should be

set after the stop bit of the previous break.

Software wait until TC=1

Software

enables the

USART

Software waits until TXE=1

and writes F2 into DR

Idle preamble Frame 1 Frame 2 Frame 3

Set by hardware

set by hardware

cleared by software

set by hardware

cleared by software

Software waits until TXE=1

and writes F1 into DR

Software waits until TXE=1

and writes F1 into DR

TC is not set

because TXE=0

TC is not set

because TXE=1

USART_DR

TC flag

TXE flag

TX line

set

by hardware

TC is not set

because TXE=0

F1 F2 F3

MS48961V1

Loading...

Loading...