Cryptographic processor (CRYP) RM0033

520/1381 RM0033 Rev 9

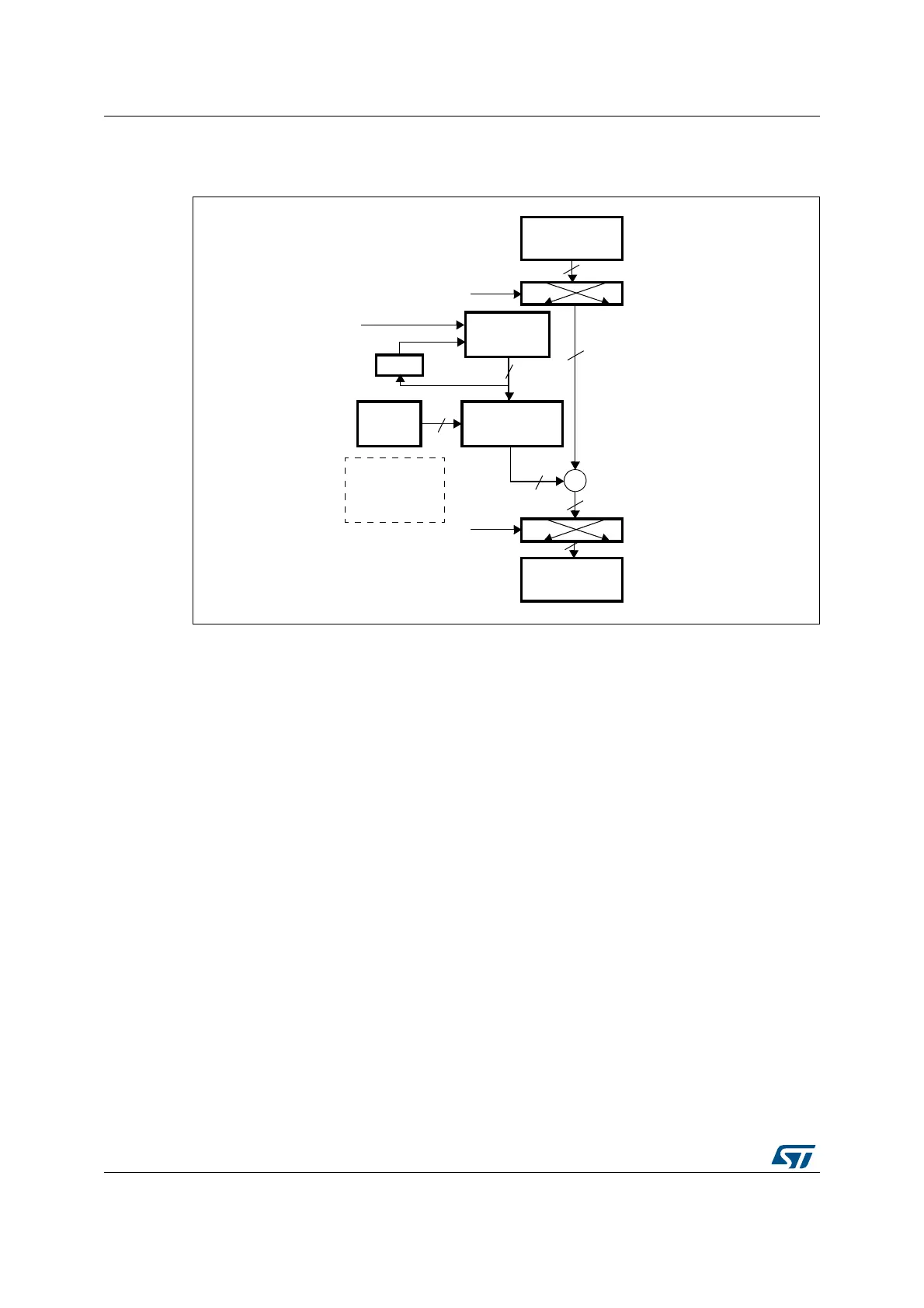

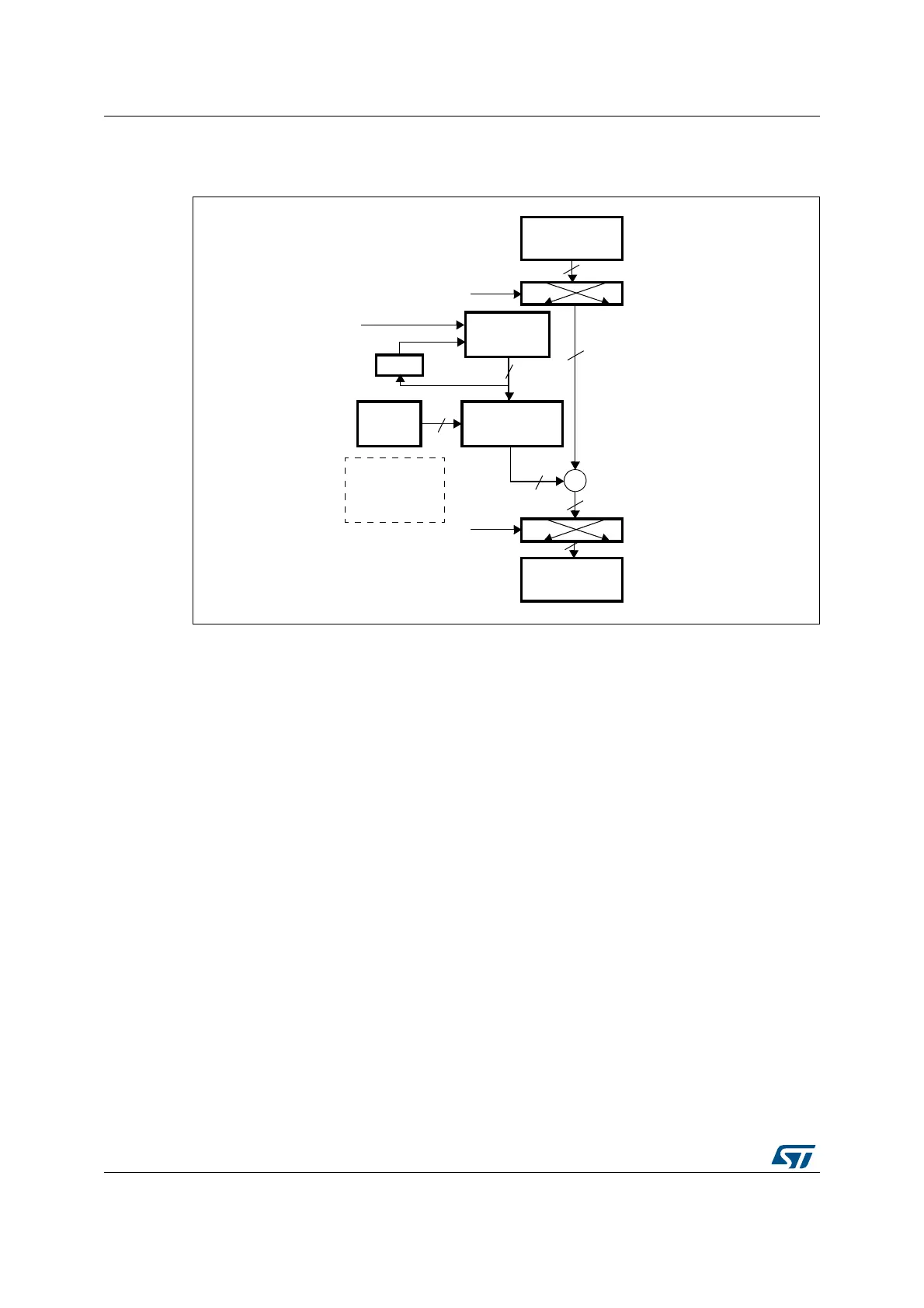

Figure 204 and Figure 205 illustrate AES-CTR encryption and decryption, respectively.

Figure 204. AES-CTR mode encryption

1. K: key; C: cipher text; I: input Block; o: output block; Ps: plain text before swapping (when decoding) or

after swapping (when encoding); Cs: cipher text after swapping (when decoding) or before swapping (when

encoding); P: plain text; IV: Initialization vectors.

IN FIFO

AEA, encrypt

P, 1 2 8 b i t s

OUT FIFO

Cs, 128 bit

plaintext P

ciphertext C

swapping

+

IV0...1(L/R)

O, 128 bits

I, 128 bits

AHB2 data write

(before CRYP

is enabled)

(I + 1) is written

back into IV

at same time

than C is pushed

in OUT FIFO

swapping

C, 128 bits

DATATYPE

DATATYPE

K0...3

128, 192

or 256

Ps, 128 bits

+1

ai16073b

Loading...

Loading...