Random number generator (RNG) RM0033

546/1381 RM0033 Rev 9

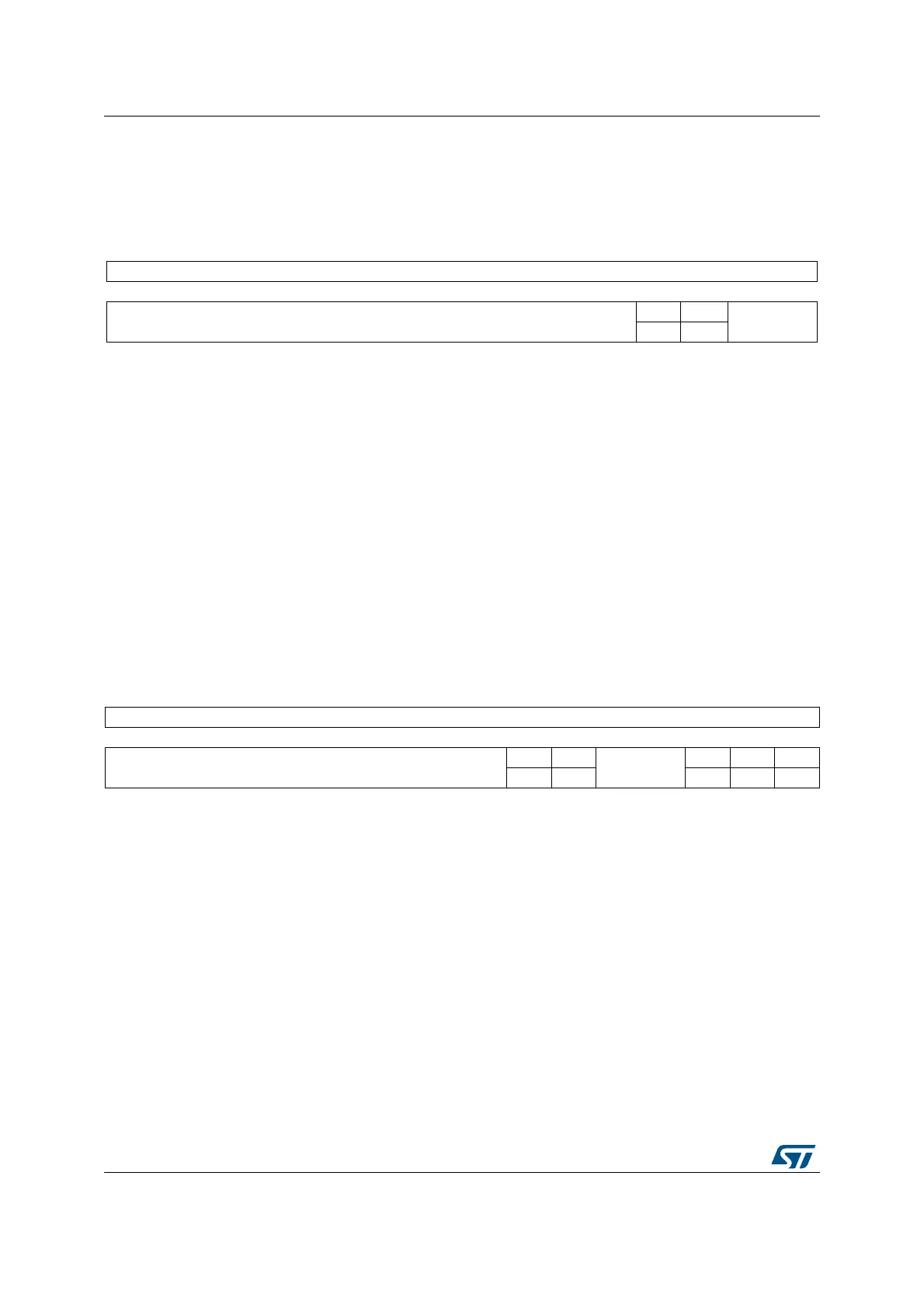

20.4.1 RNG control register (RNG_CR)

Address offset: 0x00

Reset value: 0x0000 0000

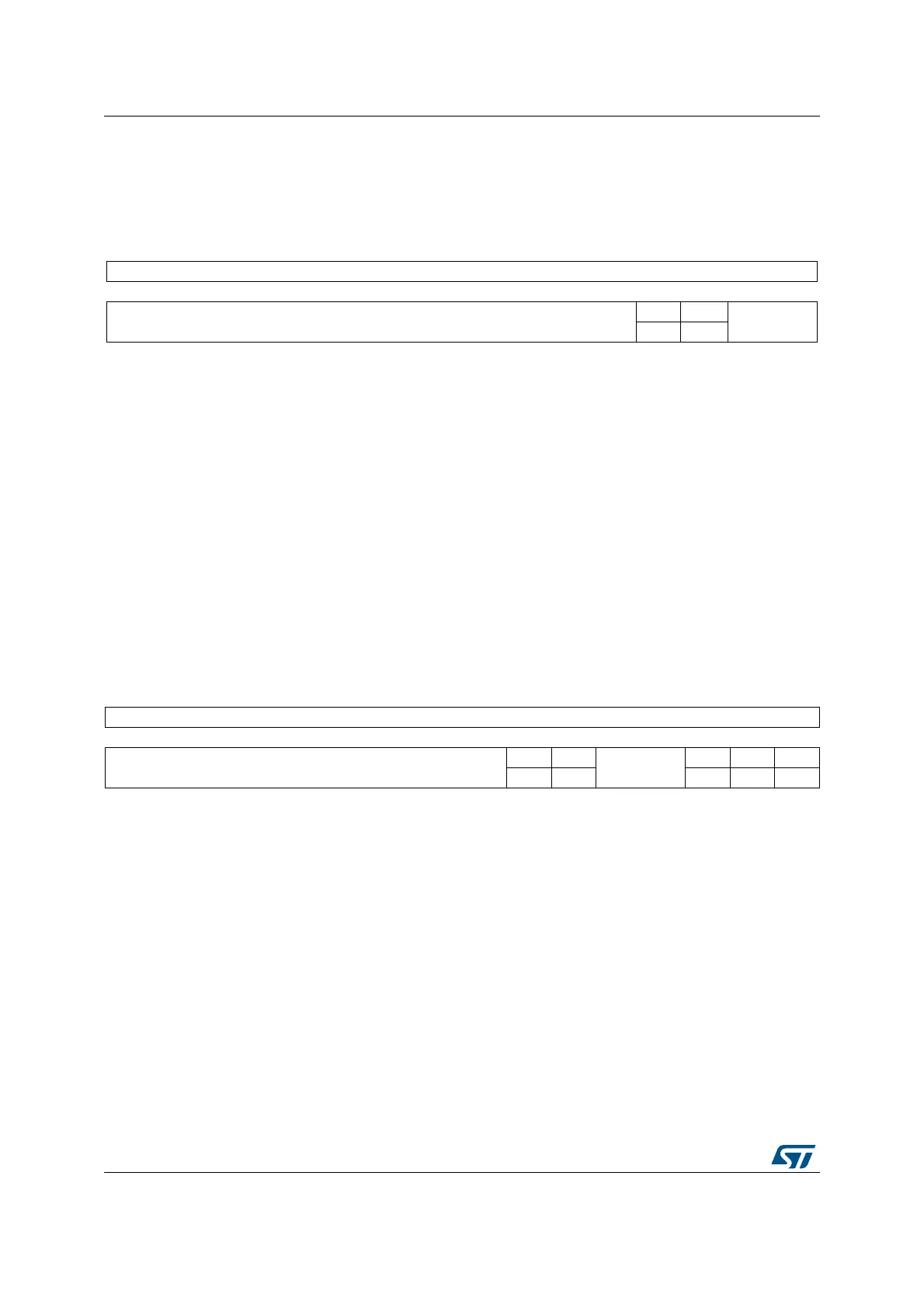

20.4.2 RNG status register (RNG_SR)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

IE RNGEN

Reserved

rw rw

Bits 31:4 Reserved, must be kept at reset value

Bit 3 IE: Interrupt enable

0: RNG Interrupt is disabled

1: RNG Interrupt is enabled. An interrupt is pending as soon as DRDY=1 or SEIS=1 or

CEIS=1 in the RNG_SR register.

Bit 2 RNGEN: Random number generator enable

0: Random number generator is disabled

1: random Number Generator is enabled.

Bits 1:0 Reserved, must be kept at reset value

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

SEIS CEIS

Reserved

SECS CECS DRDY

rc_w0 rc_w0 r r r

Bits 31:3 Reserved, must be kept at reset value

Bit 6 SEIS: Seed error interrupt status

This bit is set at the same time as SECS, it is cleared by writing it to 0.

0: No faulty sequence detected

1: One of the following faulty sequences has been detected:

– More than 64 consecutive bits at the same value (0 or 1)

– More than 32 consecutive alternances of 0 and 1 (0101010101...01)

An interrupt is pending if IE = 1 in the RNG_CR register.

Bit 5 CEIS: Clock error interrupt status

This bit is set at the same time as CECS, it is cleared by writing it to 0.

0: The RNG_CLK clock was correctly detected

1: The RNG_CLK was not correctly detected (f

RNG_CLK

< f

HCLK

/16)

An interrupt is pending if IE = 1 in the RNG_CR register.

Bits 4:3 Reserved, must be kept at reset value

Loading...

Loading...