RM0033 Rev 9 777/1381

RM0033 Secure digital input/output interface (SDIO)

791

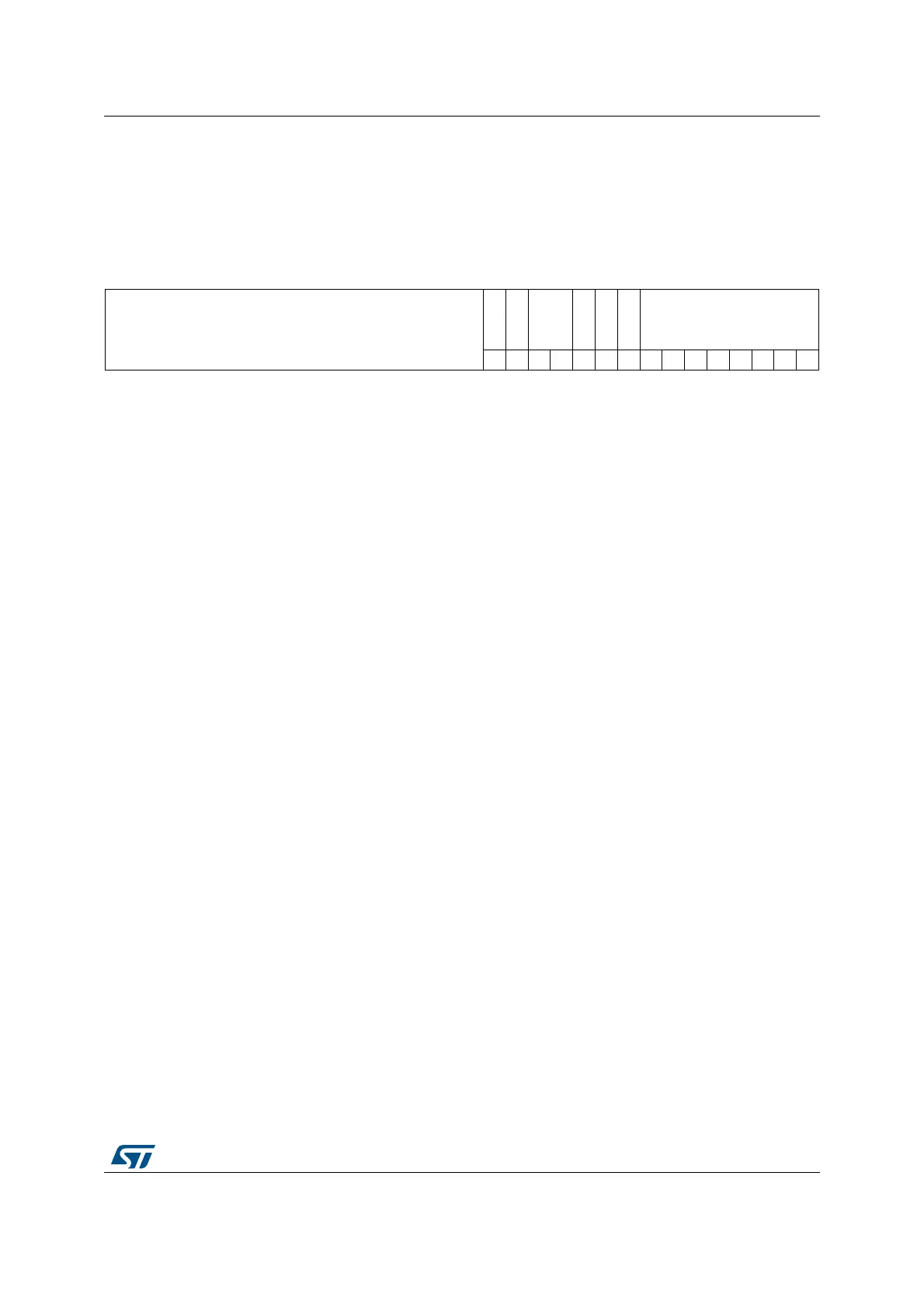

26.9.2 SDI clock control register (SDIO_CLKCR)

Address offset: 0x04

Reset value: 0x0000 0000

The SDIO_CLKCR register controls the SDIO_CK output clock.

313029282726252423222120191817161514131211109876543210

Reserved

HWFC_EN

NEGEDGE

WID

BUS

BYPASS

PWRSAV

CLKEN

CLKDIV

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:15 Reserved, must be kept at reset value

Bit 14 HWFC_EN: HW Flow Control enable

0b: HW Flow Control is disabled

1b: HW Flow Control is enabled

When HW Flow Control is enabled, the meaning of the TXFIFOE and RXFIFOF interrupt

signals, see SDIO Status register definition in Section 26.9.11.

Bit 13 NEGEDGE:SDIO_CK dephasing selection bit

0b: SDIO_CK generated on the rising edge of the master clock SDIOCLK

1b: SDIO_CK generated on the falling edge of the master clock SDIOCLK

Bits 12:11 WIDBUS: Wide bus mode enable bit

00: Default bus mode: SDIO_D0 used

01: 4-wide bus mode: SDIO_D[3:0] used

10: 8-wide bus mode: SDIO_D[7:0] used

Bit 10 BYPASS: Clock divider bypass enable bit

0: Disable bypass: SDIOCLK is divided according to the CLKDIV value before driving the

SDIO_CK output signal.

1: Enable bypass: SDIOCLK directly drives the SDIO_CK output signal.

Bit 9 PWRSAV: Power saving configuration bit

For power saving, the SDIO_CK clock output can be disabled when the bus is idle by setting

PWRSAV:

0: SDIO_CK clock is always enabled

1: SDIO_CK is only enabled when the bus is active

Bit 8 CLKEN: Clock enable bit

0: SDIO_CK is disabled

1: SDIO_CK is enabled

Bits 7:0 CLKDIV: Clock divide factor

This field defines the divide factor between the input clock (SDIOCLK) and the output clock

(SDIO_CK): SDIO_CK frequency = SDIOCLK / [CLKDIV + 2].

Note: In order to have a duty cycle of 50% it is recommended to select even values of

CLKDIV.

Loading...

Loading...