RM0033 Rev 9 563/1381

RM0033 Hash processor (HASH)

569

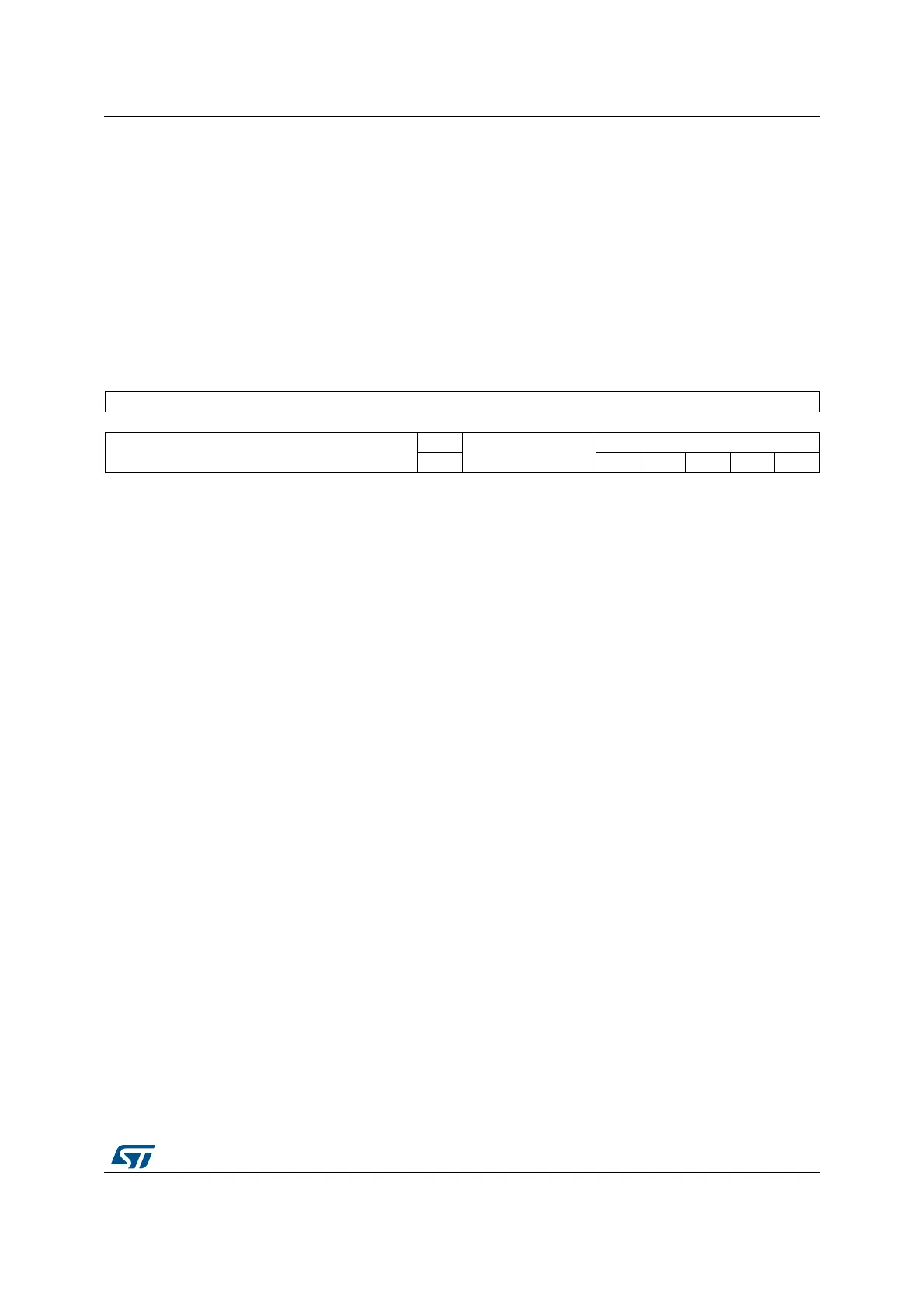

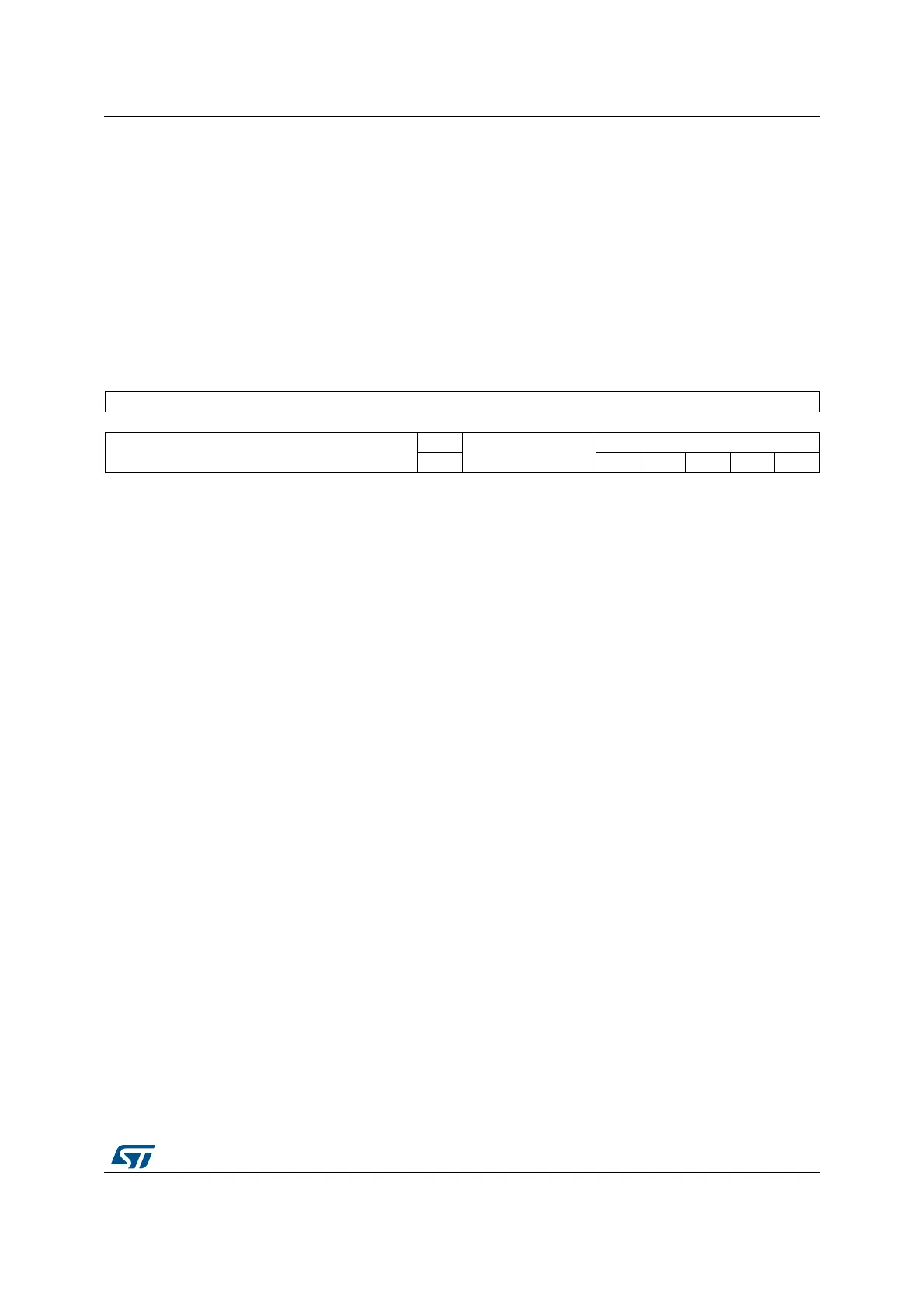

21.4.3 HASH start register (HASH_STR)

Address offset: 0x08

Reset value: 0x0000 0000

The HASH_STR register has two functions:

• It is used to define the number of valid bits in the last word of the message entered in

the hash processor (that is the number of valid least significant bits in the last data

written into the HASH_DIN register)

• It is used to start the processing of the last block in the message by writing the DCAL

bit to 1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

Reserved

DCAL

Reserved

NBLW

w rwrwrwrwrw

Bits 31:9 Reserved, forced by hardware to 0.

Bit 8 DCAL: Digest calculation

Writing this bit to 1 starts the message padding, using the previously written

value of NBLW, and starts the calculation of the final message digest with all data

words written to the IN FIFO since the INIT bit was last written to 1.

Reading this bit returns 0.

Note

Bits 7:5 Reserved, forced by hardware to 0.

Bits 4:0 NBLW: Number of valid bits in the last word of the message in the bit string

organization of hash processor

When these bits are written and DCAL is at ‘0’, they take the value on the AHB

databus:

0x00: All 32 bits of the last data written in the bit string organization of hash

processor (after data swapping) are valid.

0x01: Only bit [31] of the last data written in the bit string organization of hash

processor (after data swapping) are valid

0x02: Only bits [31:30] of the last data written in the bit string organization of

hash processor (after data swapping) are valid

0x03: Only bits [31:29] of the last data written in the bit string organization of

hash processor (after data swapping) are valid

...

0x1F: Only bits [0] of the last data written in the bit string organization of hash

processor (after data swapping) are valid

When these bits are written and DCAL is at ‘1’, the bitfield is not changed.

Reading them returns the last value written to NBLW.

Note: These bits must be configured before setting the DCAL bit, else they are not

taken into account. Especially, it is not possible to configure NBLW and set

DCAL at the same time.

Loading...

Loading...