System configuration controller (SYSCFG) RM0033

160/1381 RM0033 Rev 9

7.2.2 SYSCFG peripheral mode configuration register (SYSCFG_PMC)

Address offset: 0x04

Reset value: 0x0000 0000

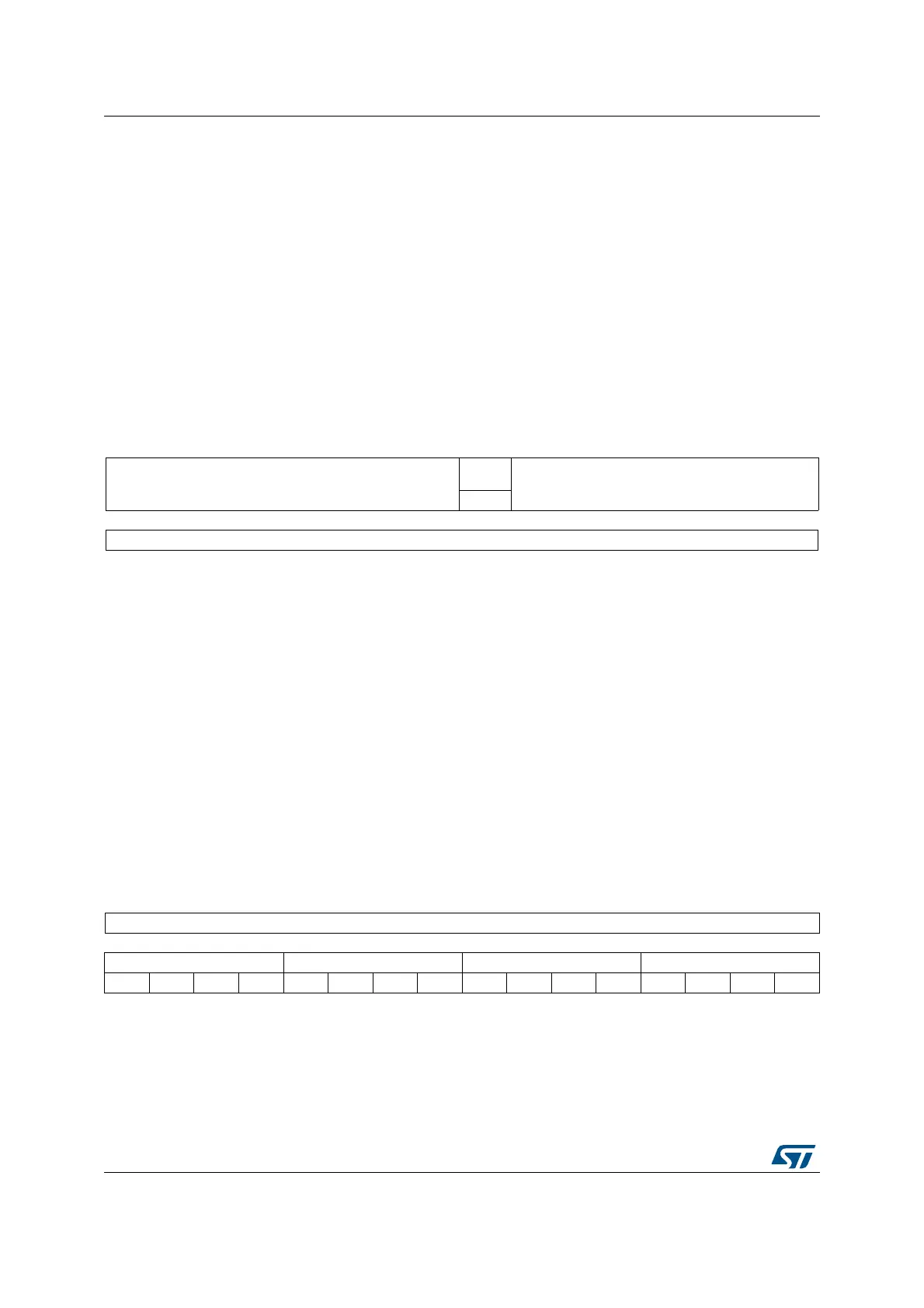

7.2.3 SYSCFG external interrupt configuration register 1

(SYSCFG_EXTICR1)

Address offset: 0x08

Reset value: 0x0000

Bits 31:2 Reserved

Bits 1:0 MEM_MODE: Memory mapping selection

Set and cleared by software. This bit controls the memory internal mapping at address

0x0000 0000. After reset these bits take on the memory mapping selected by the BOOT pins.

00: Main Flash memory mapped at 0x0000 0000

01: System Flash memory mapped at 0x0000 0000

10: FSMC Bank1 (NOR/PSRAM 1 and 2) mapped at 0x0000 0000

11: Embedded SRAM (112kB) mapped at 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

MII_RMII

_SEL

Reserved

rw

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

Bits 31:24 Reserved

Bit 23 MII_RMII_SEL: Ethernet PHY interface selection

Set and Cleared by software.These bits control the PHY interface for the Ethernet MAC.

0: MII interface is selected

1: RMII PHY interface is selected

Note: This configuration must be done while the MAC is under reset and before enabling the

MAC clocks.

Bits 22:0 Reserved

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

1514131211109876543210

EXTI3[3:0] EXTI2[3:0] EXTI1[3:0] EXTI0[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...