RM0033 Rev 9 723/1381

RM0033 Serial peripheral interface (SPI)

734

slave transmission mode, this flag is not reliable and I

2

S needs to be switched off and

switched on before resuming the communication.

In reception mode, this flag is refreshed when data are received into SPI_DR. It indicates

from which channel side data have been received. Note that in case of error (like OVR) this

flag becomes meaningless and the I

2

S should be reset by disabling and then enabling it

(with configuration if it needs changing).

This flag has no meaning in the PCM standard (for both Short and Long frame modes).

When the OVR or UDR flag in the SPI_SR is set and the ERRIE bit in SPI_CR2 is also set,

an interrupt is generated. This interrupt can be cleared by reading the SPI_SR status

register (once the interrupt source has been cleared).

25.4.7 Error flags

There are two error flags for the I

2

S cell.

Underrun flag (UDR)

In slave transmission mode this flag is set when the first clock for data transmission appears

while the software has not yet loaded any value into SPI_DR. It is available when the

I2SMOD bit in SPI_I2SCFGR is set. An interrupt may be generated if the ERRIE bit in

SPI_CR2 is set.

The UDR bit is cleared by a read operation on the SPI_SR register.

Overrun flag (OVR)

This flag is set when data are received and the previous data have not yet been read from

SPI_DR. As a result, the incoming data are lost. An interrupt may be generated if the ERRIE

bit is set in SPI_CR2.

In this case, the receive buffer contents are not updated with the newly received data from

the transmitter device. A read operation to the SPI_DR register returns the previous

correctly received data. All other subsequently transmitted half-words are lost.

Clearing the OVR bit is done by a read operation on the SPI_DR register followed by a read

access to the SPI_SR register.

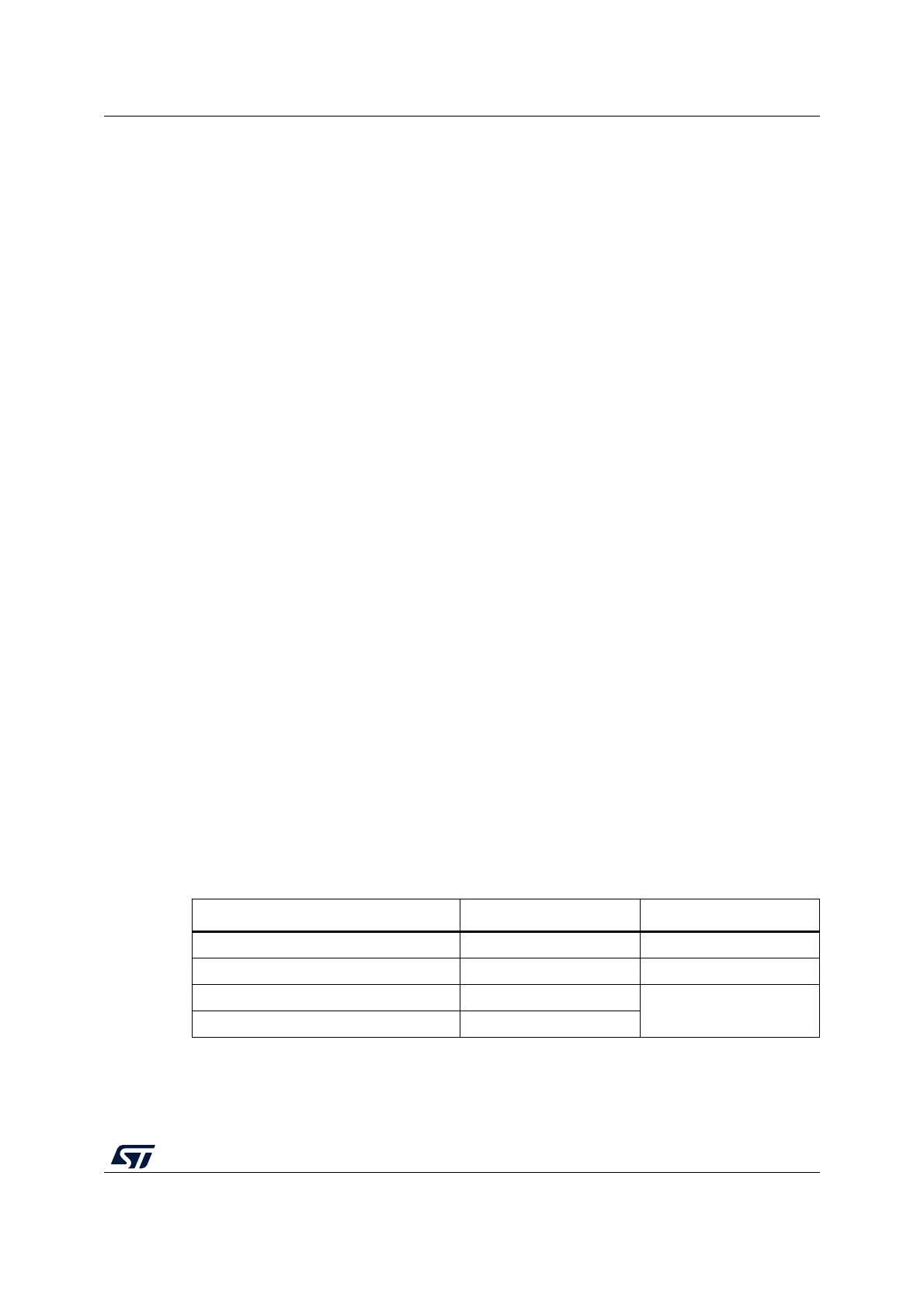

25.4.8 I

2

S interrupts

Table 101 provides the list of I

2

S interrupts.

Table 101. I

2

S interrupt requests

Interrupt event Event flag Enable Control bit

Transmit buffer empty flag TXE TXEIE

Receive buffer not empty flag RXNE RXNEIE

Overrun error OVR

ERRIE

Underrun error UDR

Loading...

Loading...