Memory and bus architecture RM0033

52/1381 RM0033 Rev 9

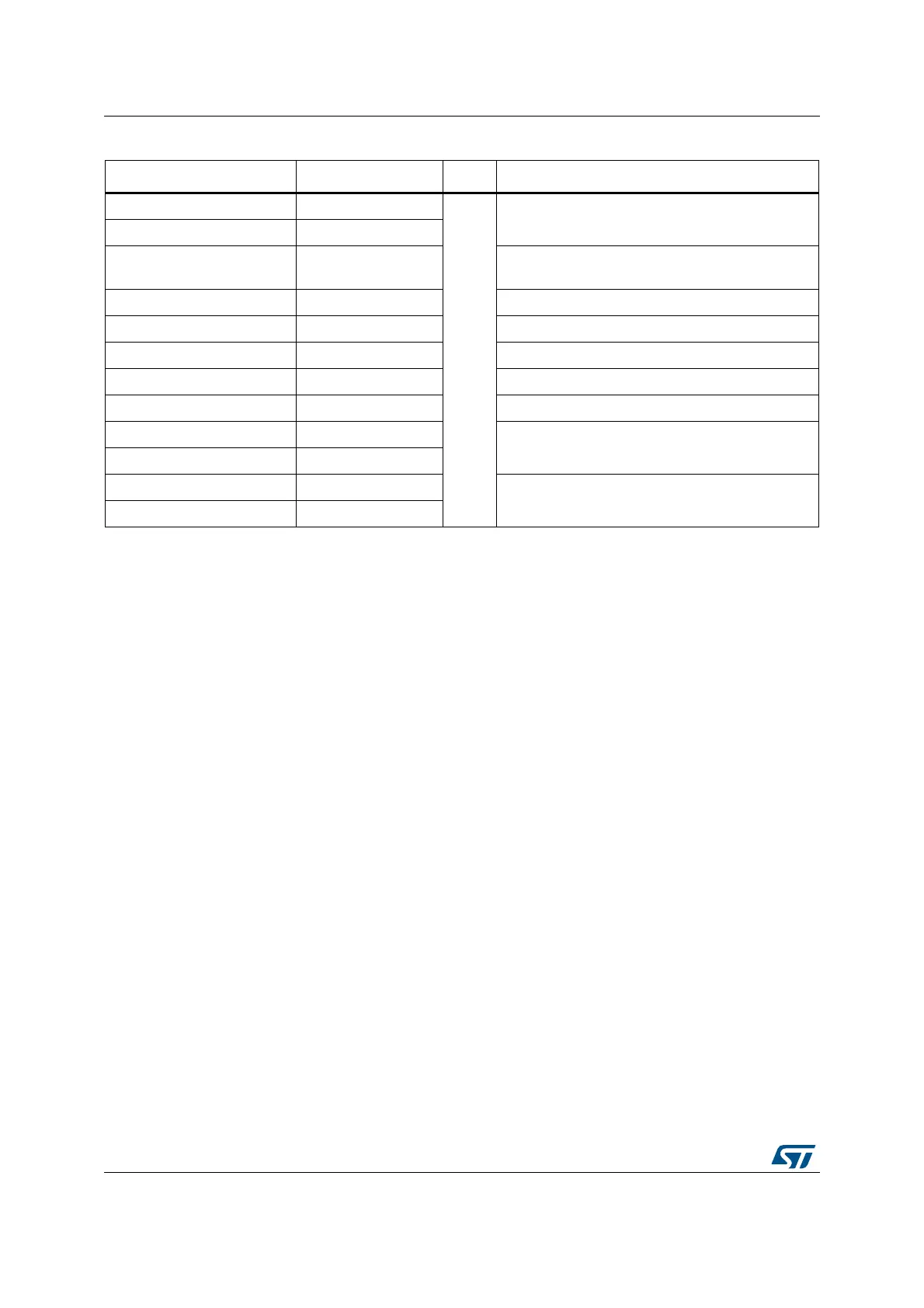

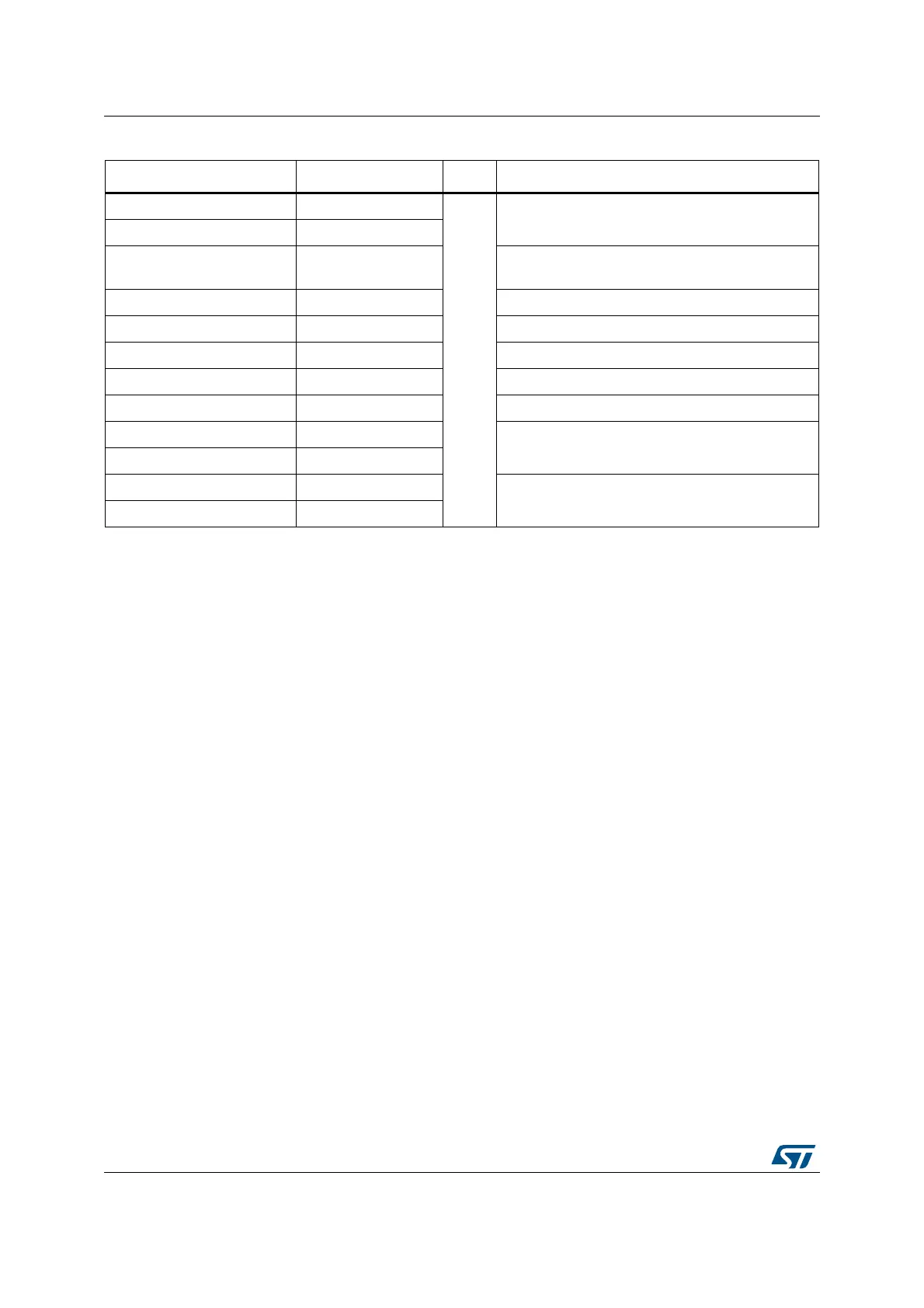

0x4001 4800 - 0x4001 4BFF TIM11

APB2

Section 15.5.12: TIM10/11/13/14 register map on

page 482

0x4001 4400 - 0x4001 47FF TIM10

0x4001 4000 - 0x4001 43FF TIM9

Section 15.4.14: TIM9/12 register map on

page 472

0x4001 3C00 - 0x4001 3FFF EXTI Section 8.3.7: EXTI register map on page 175

0x4001 3800 - 0x4001 3BFF SYSCFG Section 7.2.8: SYSCFG register map on page 163

0x4001 3000 - 0x4001 33FF SPI1 Section 25.5.10: SPI register map on page 734

0x4001 2C00 - 0x4001 2FFF SDIO Section 26.9.16: SDIO register map on page 790

0x4001 2000 - 0x4001 23FF ADC1 - ADC2 - ADC3 Section 10.13.18: ADC register map on page 253

0x4001 1400 - 0x4001 17FF USART6

Section 24.6.8: USART register map on page 681

0x4001 1000 - 0x4001 13FF USART1

0x4001 0400 - 0x4001 07FF TIM8

Section 13.4.21: TIM1 and TIM8 register map on

page 374

0x4001 0000 - 0x4001 03FF TIM1

Table 1. STM32F20x and STM32F21x register boundary addresses (continued)

Boundary address Peripheral Bus Register map

Loading...

Loading...