Ethernet (ETH): media access control (MAC) with DMA controller RM0033

954/1381 RM0033 Rev 9

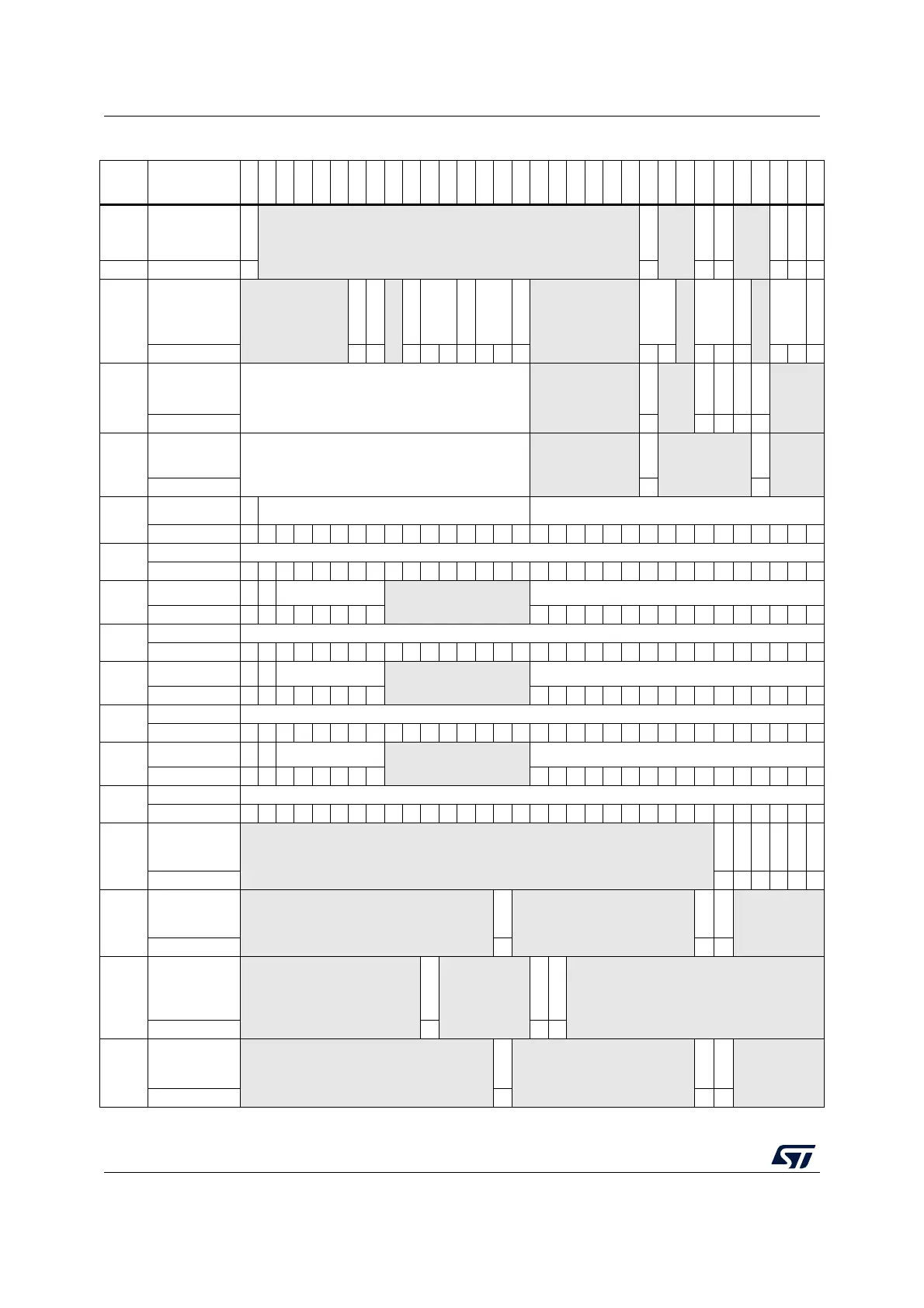

0x2C

ETH_

MACPMTCSR

WFFRPR

Reserved

GU

Reserved

WFR

MPR

Reserved

WFE

MPE

PD

Reset value 0 000000

0x34

ETH_

MACDBGR

Reserved

TFF

TFNEGU

Reserved

TFWA

TFRS

MTP

MTFCS

MMTEA

Reserved

RFFL

Reserved

RFRCS

RFWRA

Reserved

MSFRWCS

MMRPEA

Reset value 00 0000000 00 000 000

0x38

ETH_MACSR

Reserved

TSTS

Reserved

MMCTS

MMCRS

MMCS

PMTS

Reserve

d

Reset value 00000

0x3C

ETH_MACIMR

Reserved

TSTIM

Reserved

PMTIM

Reserve

d

Reset value 00

0x40

ETH_MACA0HR

MO

Reserved MACA0H

Reset value 10000000000000001111111111111111

0x44

ETH_MACA0LR MACA0L

Reset value 11111111111111111111111111111111

0x48

ETH_MACA1HR

AE

SA

MBC[6:0]

Reserved

MACA1H

Reset value 00000000 1111111111 111111

0x4C

ETH_MACA1LR MACA1L

Reset value 11111111111111111111111111111111

0x50

ETH_MACA2HR

AE

SA

MBC

Reserved

MACA2H

Reset value 00000000 1111111111 111111

0x54

ETH_MACA2LR MACA2L

Reset value 11111111111111111111111111111111

0x58

ETH_MACA3HR

AE

SA

MBC

Reserved

MACA3H

Reset value 00000000 1111111111 111111

0x5C

ETH_MACA3LR MACA3L

Reset value 11111111111111111111111111111111

0x100

ETH_MMCCR

Reserved

MCFHP

MCP

MCF

ROR

CSR

CR

Reset value 000000

0x104

ETH_MMCRIR

Reserved

RGUFS

Reserved

RFAES

RFCES

Reserved

Reset value 0 0 0

0x108

ETH_MMCTIR

Reserved

TGFS

Reserved

TGFMSCS

TGFSCS

Reserved

Reset value 0 0 0

0x10C

ETH_MMCRIMR

Reserved

RGUFM

Reserved

RFAEM

RFCEM

Reserved

Reset value 0 0 0

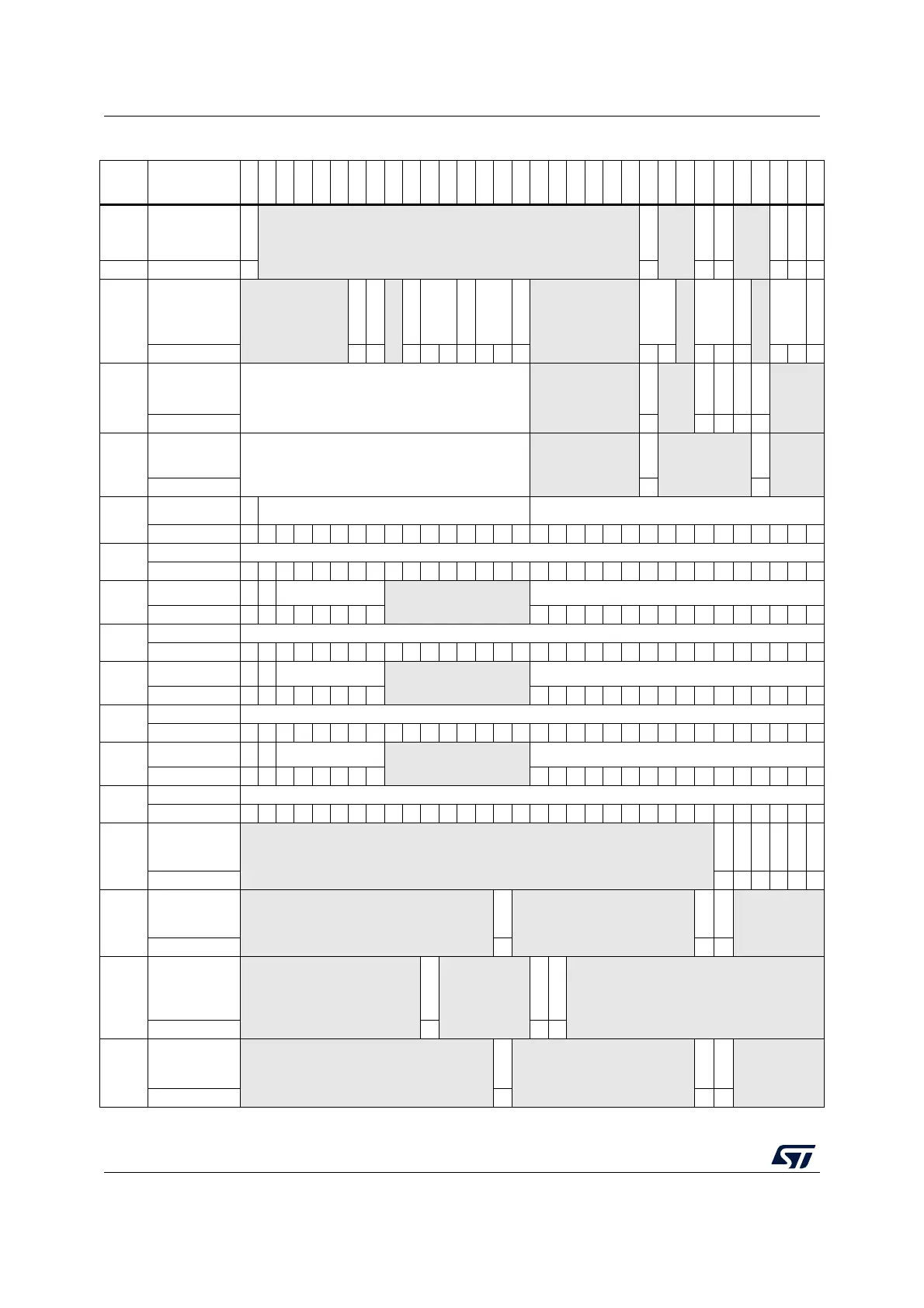

Table 148. Ethernet register map and reset values (continued)

Offset Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...