RM0033 Rev 9 1037/1381

RM0033 USB on-the-go full-speed (OTG_FS)

1097

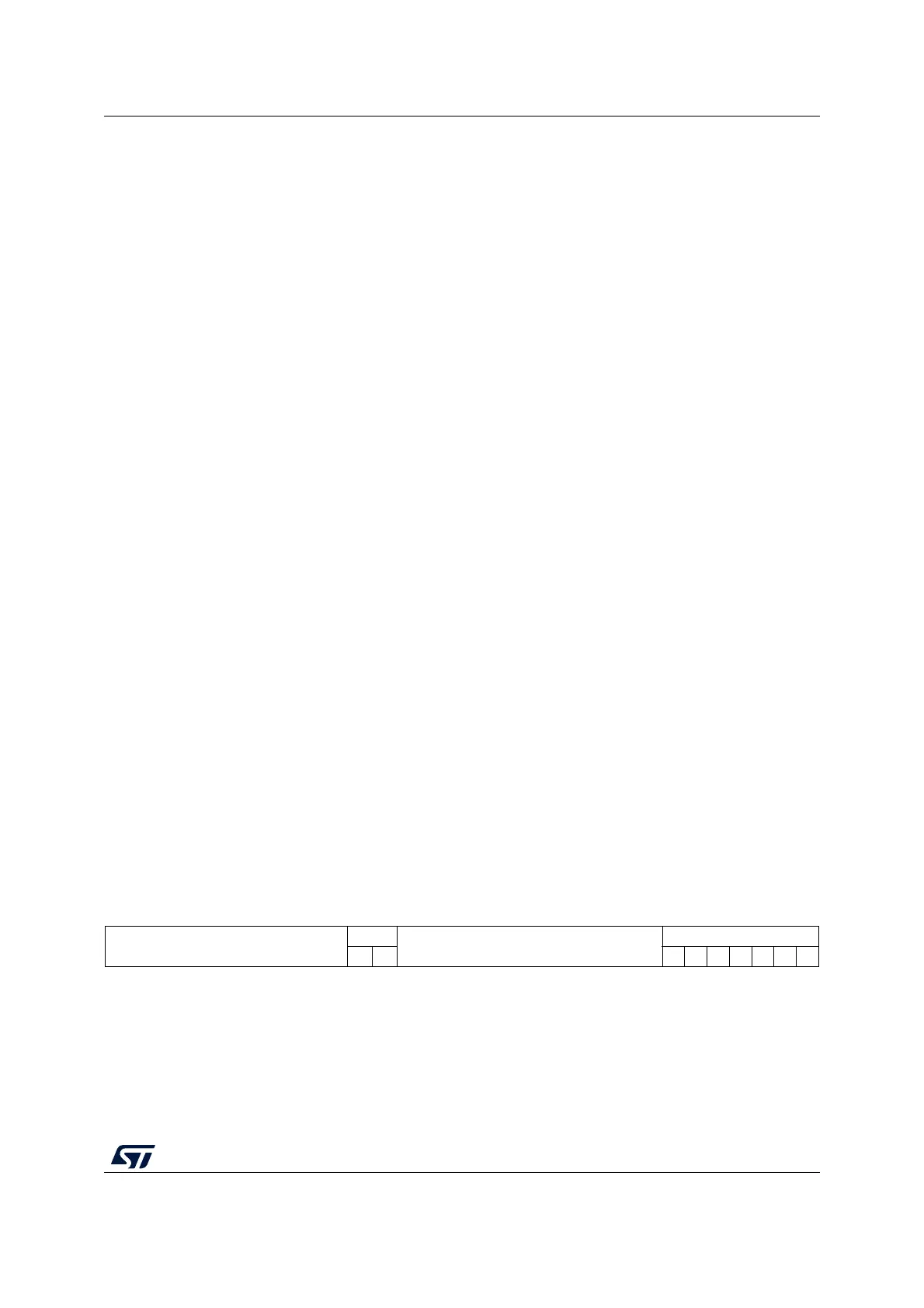

OTG_FS device IN endpoint 0 transfer size register (OTG_FS_DIEPTSIZ0)

Address offset: 0x910

Reset value: 0x0000 0000

The application must modify this register before enabling endpoint 0. Once endpoint 0 is

enabled using the endpoint enable bit in the device control endpoint 0 control registers

(EPENA in OTG_FS_DIEPCTL0), the core modifies this register. The application can only

read this register once the core has cleared the Endpoint enable bit.

Nonzero endpoints use the registers for endpoints 1–3.

Bit 8 OUTPKTERR: OUT packet error

This interrupt is asserted when the core detects an overflow or a CRC error for an OUT

packet. This interrupt is valid only when thresholding is enabled.

Bits 7:6 Reserved, must be kept at reset value.

Bit 5 STSPHSRX: Status phase received for control write

This interrupt is generated only after the core has transferred all the data that the host has

sent during the data phase of a control write transfer, to the system memory buffer. The

interrupt indicates to the application that the host has switched from data phase to the status

phase of a control write transfer. The application can use this interrupt to ACK or STALL the

status phase, after it has decoded the data phase.

Bit 4 OTEPDIS: OUT token received when endpoint disabled

Applies only to control OUT endpoints.

Indicates that an OUT token was received when the endpoint was not yet enabled. This

interrupt is asserted on the endpoint for which the OUT token was received.

Bit 3 STUP: SETUP phase done

Applies to control OUT endpoint only.

Indicates that the SETUP phase for the control endpoint is complete and no more back-to-

back SETUP packets were received for the current control transfer. On this interrupt, the

application can decode the received SETUP data packet.

Bit 2 Reserved, must be kept at reset value.

Bit 1 EPDISD: Endpoint disabled interrupt

This bit indicates that the endpoint is disabled per the application’s request.

Bit 0 XFRC: Transfer completed interrupt

This field indicates that the programmed transfer is complete on the AHB as well as on the

USB, for this endpoint.

313029282726252423222120191817161514131211109876543210

Reserved

PKTCNT

Reserved

XFRSIZ

rw rw rw rw rw rw rw rw rw

Loading...

Loading...