RM0033 Rev 9 1171/1381

RM0033 USB on-the-go high-speed (OTG_HS)

1260

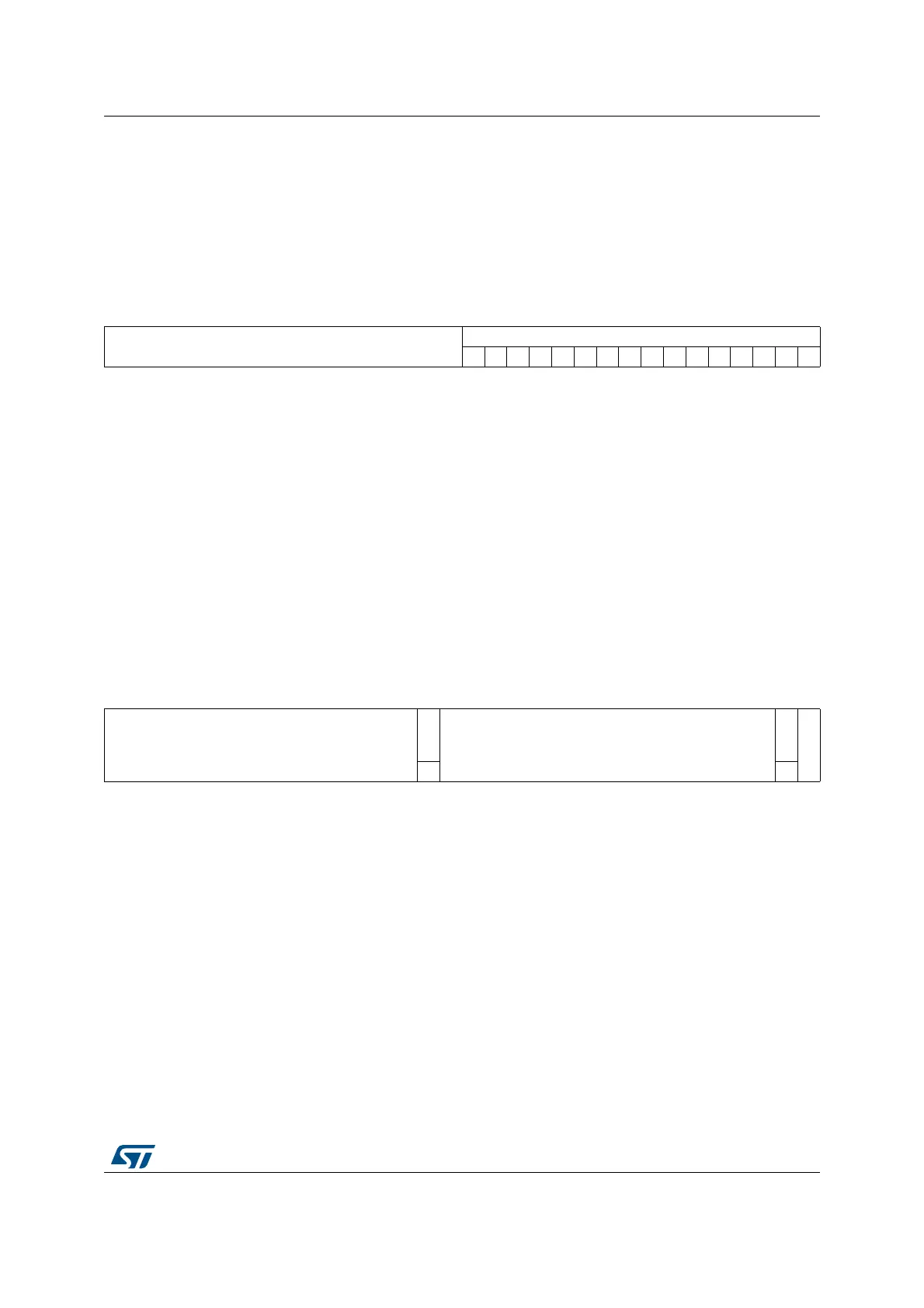

OTG_HS device IN endpoint FIFO empty interrupt mask register:

(OTG_HS_DIEPEMPMSK)

Address offset: 0x834

Reset value: 0x0000 0000

This register is used to control the IN endpoint FIFO empty interrupt generation

(TXFE_OTG_HS_DIEPINTx).

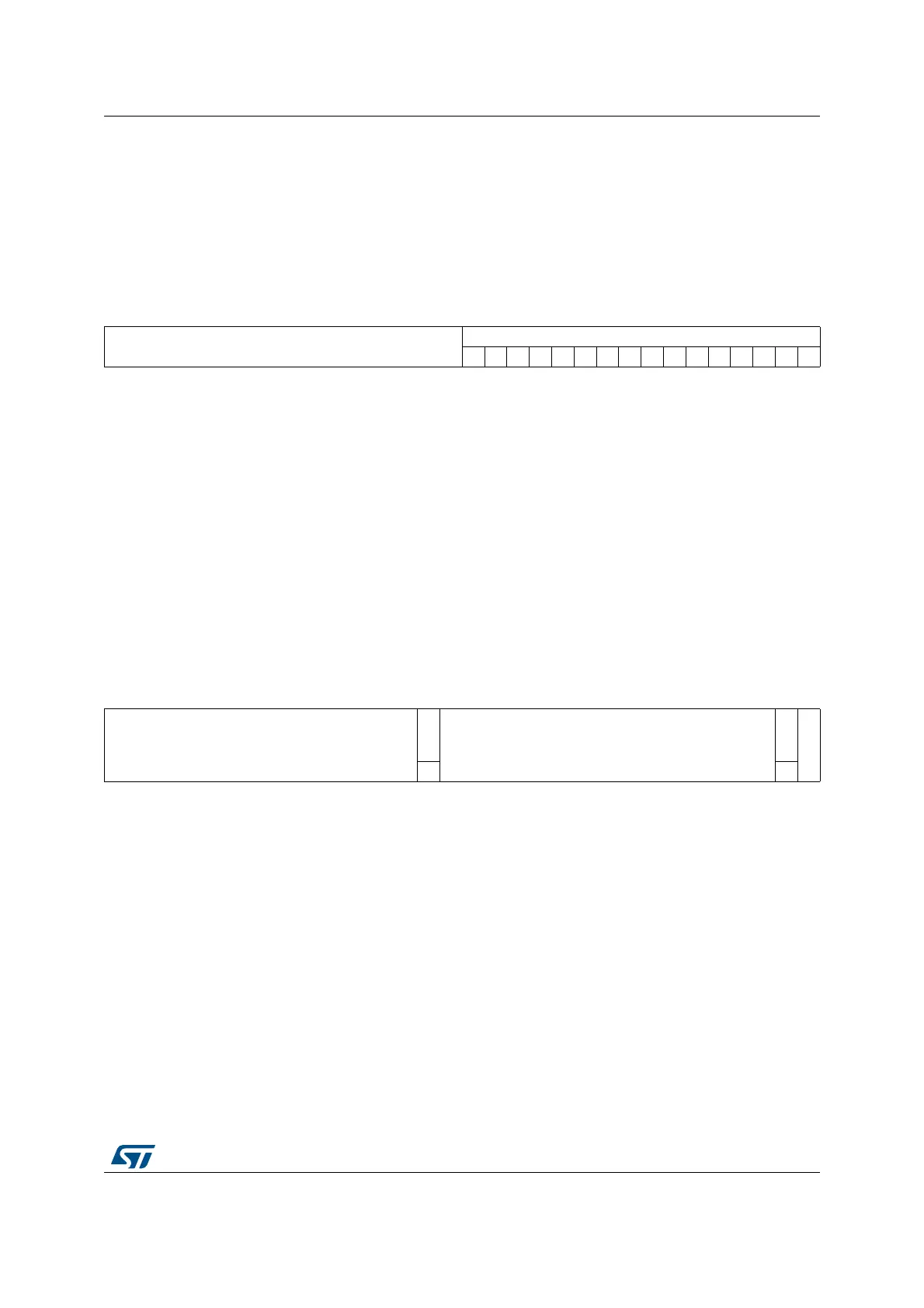

OTG_HS device each endpoint interrupt register (OTG_HS_DEACHINT)

Address offset: 0x0838

Reset value: 0x0000 0000

There is one interrupt bit for endpoint 1 IN and one interrupt bit for endpoint 1 OUT.

313029282726252423222120191817161514131211109876543210

Reserved

INEPTXFEM

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 INEPTXFEM: IN EP Tx FIFO empty interrupt mask bits

These bits act as mask bits for OTG_HS_DIEPINTx.

TXFE interrupt one bit per IN endpoint:

Bit 0 for IN endpoint 0, bit 15 for IN endpoint 15

0: Masked interrupt

1: Unmasked interrupt

313029282726252423222120191817161514131211109876543210

Reserved

OEP1INT

Reserved

IEP1INT

Reserved

r r

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 OEP1INT: OUT endpoint 1 interrupt bit

Bits 16:2 Reserved, must be kept at reset value.

Bit 1 IEP1INT: IN endpoint 1interrupt bit

Bit 0 Reserved, must be kept at reset value.

Loading...

Loading...