USB on-the-go high-speed (OTG_HS) RM0033

1172/1381 RM0033 Rev 9

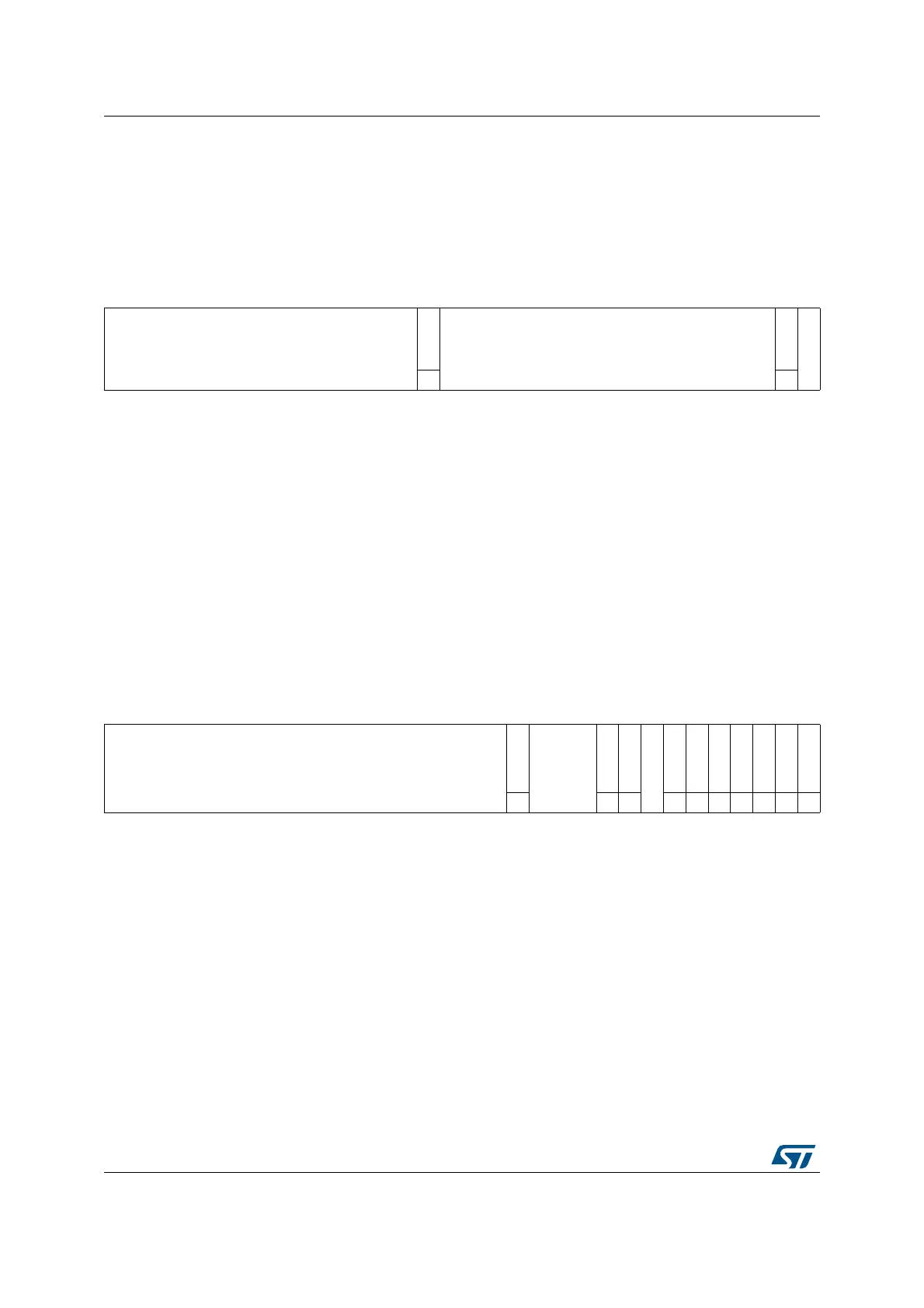

OTG_HS device each endpoint interrupt register mask

(OTG_HS_DEACHINTMSK)

Address offset: 0x083C

Reset value: 0x0000 0000

There is one interrupt bit for endpoint 1 IN and one interrupt bit for endpoint 1 OUT.

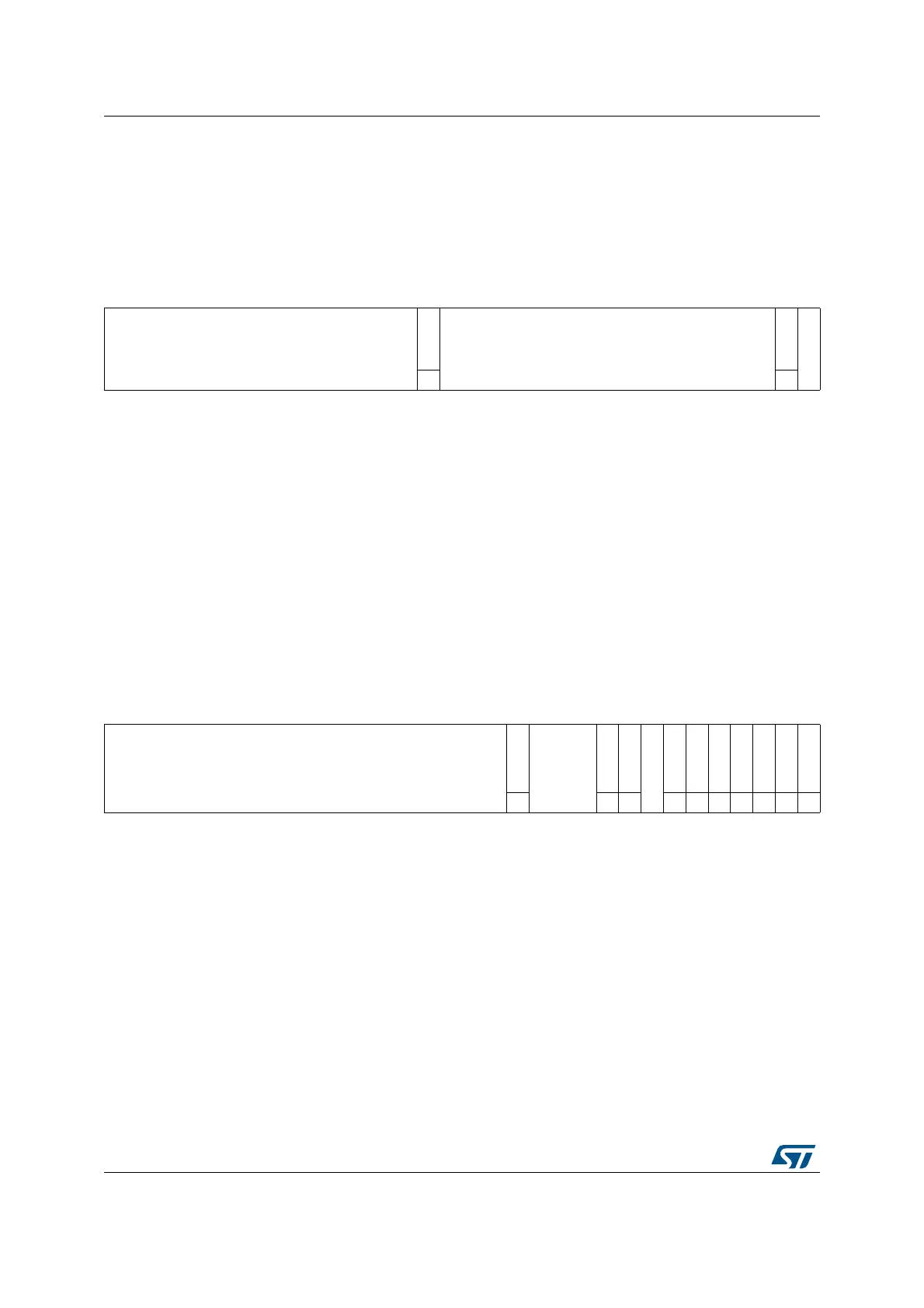

OTG_HS device each in endpoint-1 interrupt register

(OTG_HS_DIEPEACHMSK1)

Address offset: 0x844

Reset value: 0x0000 0000

313029282726252423222120191817161514131211109876543210

Reserved

OEP1INTM

Reserved

IEP1INTM

Reserved

rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 OEP1INTM: OUT Endpoint 1 interrupt mask bit

Bits 16:2 Reserved, must be kept at reset value.

Bit 1 IEP1INTM: IN Endpoint 1 interrupt mask bit

Bit 0 Reserved, must be kept at reset value.

313029282726252423222120191817161514131211109876543210

Reserved

NAKM

Reserved

BIM

TXFURM

Reserved

INEPNEM

INEPNMM

ITTXFEMSK

TOM

AHBERRM

EPDM

XFRCM

rw rw rw rw rw rw rw rw rw rw

Bits 31:14 Reserved, must be kept at reset value.

Bit 13 NAKM: NAK interrupt mask

0: Masked interrupt

1: unmasked interrupt

Bit 12:10 Reserved, must be kept at reset value.

Bit 9 BIM: BNA interrupt mask

0: Masked interrupt

1: Unmasked interrupt

Bit 8 TXFURM: FIFO underrun mask

0: Masked interrupt

1: Unmasked interrupt

Bit 7 Reserved, must be kept at reset value.

Loading...

Loading...