USB on-the-go high-speed (OTG_HS) RM0033

1184/1381 RM0033 Rev 9

OTG_HS device IN endpoint 0 transfer size register (OTG_HS_DIEPTSIZ0)

Address offset: 0x910

Reset value: 0x0000 0000

The application must modify this register before enabling endpoint 0. Once endpoint 0 is

enabled using the endpoint enable bit in the device control endpoint 0 control registers

(EPENA in OTG_HS_DIEPCTL0), the core modifies this register. The application can only

read this register once the core has cleared the Endpoint enable bit.

Nonzero endpoints use the registers for endpoints 1–15.

Bit 3 STUP: SETUP phase done

Applies to control OUT endpoints only.

Indicates that the SETUP phase for the control endpoint is complete and no more back-to-

back SETUP packets were received for the current control transfer. On this interrupt, the

application can decode the received SETUP data packet.

Bit 2 AHBERR: AHB error

This is generated only in internal DMA mode when there is an AHB error during an AHB

read/write. The application can read the corresponding endpoint DMA address register to

get the error address.

Bit 1 EPDISD: Endpoint disabled interrupt

This bit indicates that the endpoint is disabled per the application’s request.

Bit 0 XFRC: Transfer completed interrupt

This field indicates that the programmed transfer is complete on the AHB as well as on the

USB, for this endpoint.

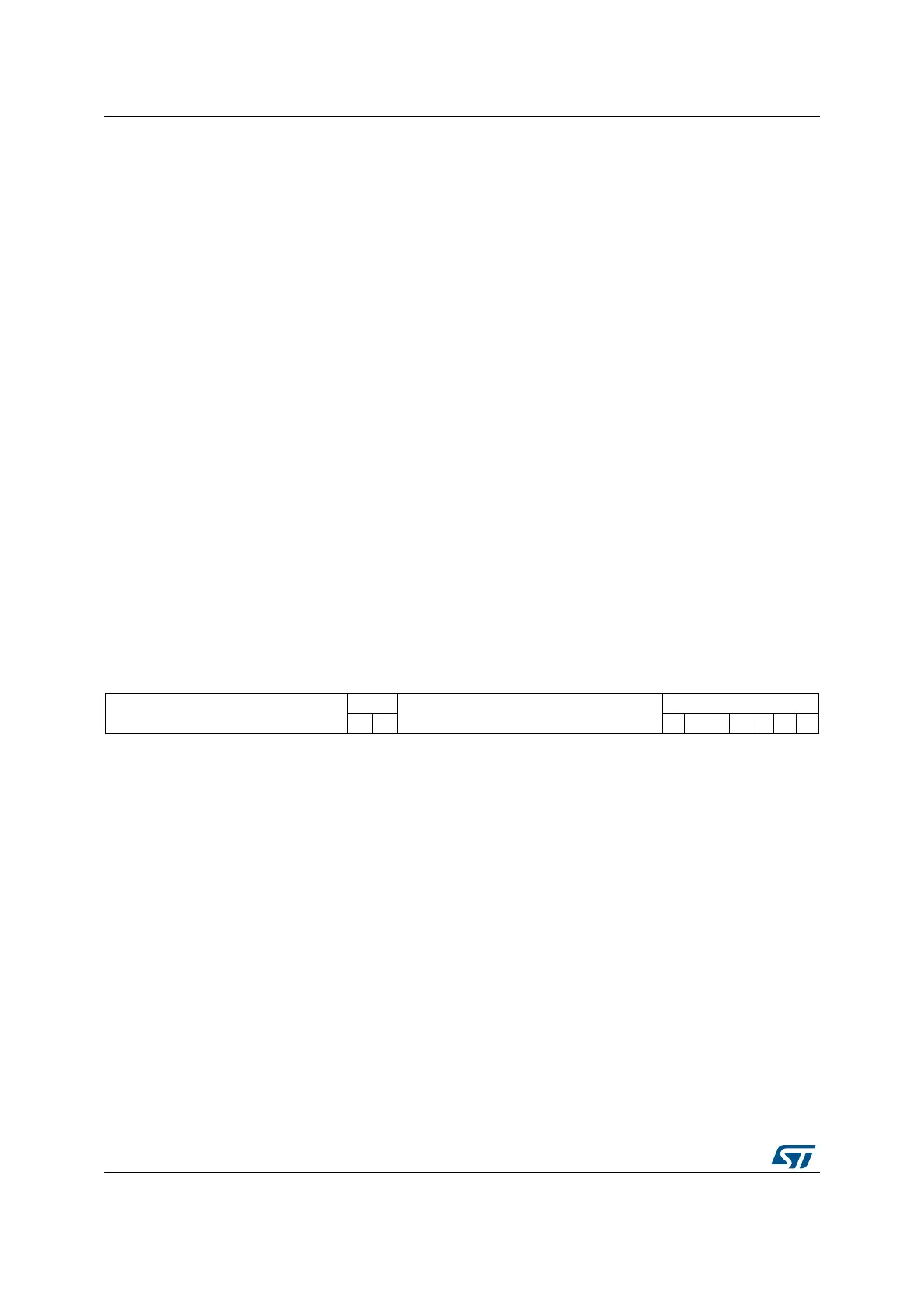

313029282726252423222120191817161514131211109876543210

Reserved

PKTCNT

Reserved

XFRSIZ

rw rw rw rw rw rw rw rw rw

Bits 31:21 Reserved, must be kept at reset value.

Bits 20:19 PKTCNT: Packet count

Indicates the total number of USB packets that constitute the Transfer Size amount of data

for endpoint 0.

This field is decremented every time a packet (maximum size or short packet) is read from

the TxFIFO.

Bits 18:7 Reserved, must be kept at reset value.

Bits 6:0 XFRSIZ: Transfer size

Indicates the transfer size in bytes for endpoint 0. The core interrupts the application only

after it has exhausted the transfer size amount of data. The transfer size can be set to the

maximum packet size of the endpoint, to be interrupted at the end of each packet.

The core decrements this field every time a packet from the external memory is written to

the TxFIFO.

Loading...

Loading...