RM0033 Rev 9 57/1381

RM0033 Memory and bus architecture

60

configured, you can check the AHB prescaler factor and clock source status values. To

make sure that the number of WS you have programmed is effective, you can read the

FLASH_ACR register.

The FLASH_ACR register is used to enable/disable the acceleration features and control

the Flash memory access time according to CPU frequency. The tables below provides the

bit map and bit descriptions for this register.

For complete information on Flash memory operations and register configurations, please

refer to the STM32F20x and STM32F21x Flash programming manual (PM0059).

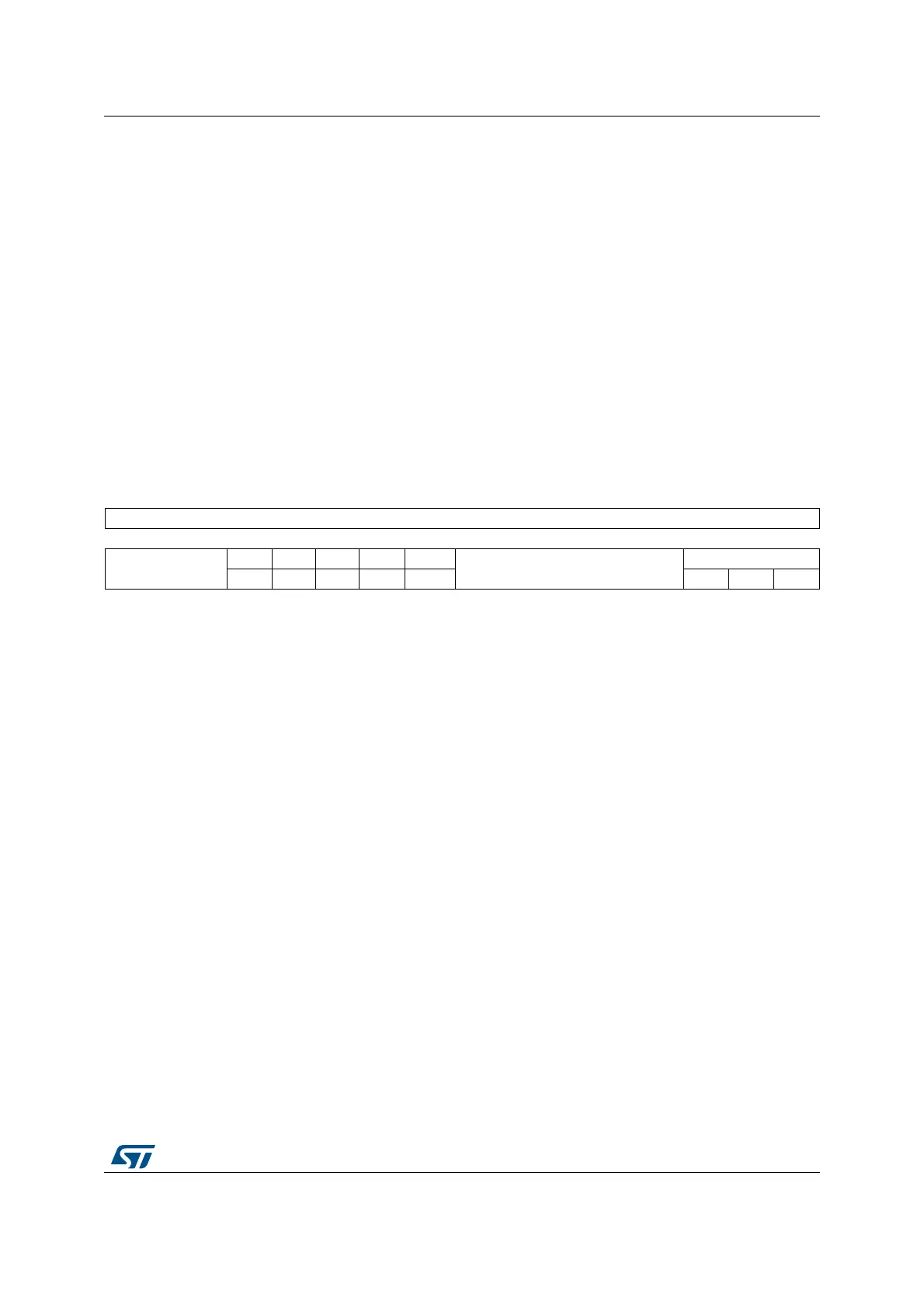

Flash access control register (FLASH_ACR)

The Flash access control register is used to enable/disable the acceleration features and

control the Flash memory access time according to CPU frequency.

Address offset: 0x00

Reset value: 0x0000 0000

Access: no wait state, word, half-word and byte access

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Reserved

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

DCRST ICRST DCEN ICEN PRFTEN

Reserved

LATENCY

rwwrwrw rw rwrwrw

Bits 31:11 Reserved, must be kept cleared.

Bit 12 DCRST: Data cache reset

0: Data cache is not reset

1: Data cache is reset

This bit can be written only when the D cache is disabled.

Bit 11 ICRST: Instruction cache reset

0: Instruction cache is not reset

1: Instruction cache is reset

This bit can be written only when the I cache is disabled.

Bit 10 DCEN: Data cache enable

0: Data cache is disabled

1: Data cache is enabled

Bit 9 ICEN: Instruction cache enable

0: Instruction cache is disabled

1: Instruction cache is enabled

Loading...

Loading...