RM0033 Rev 9 951/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

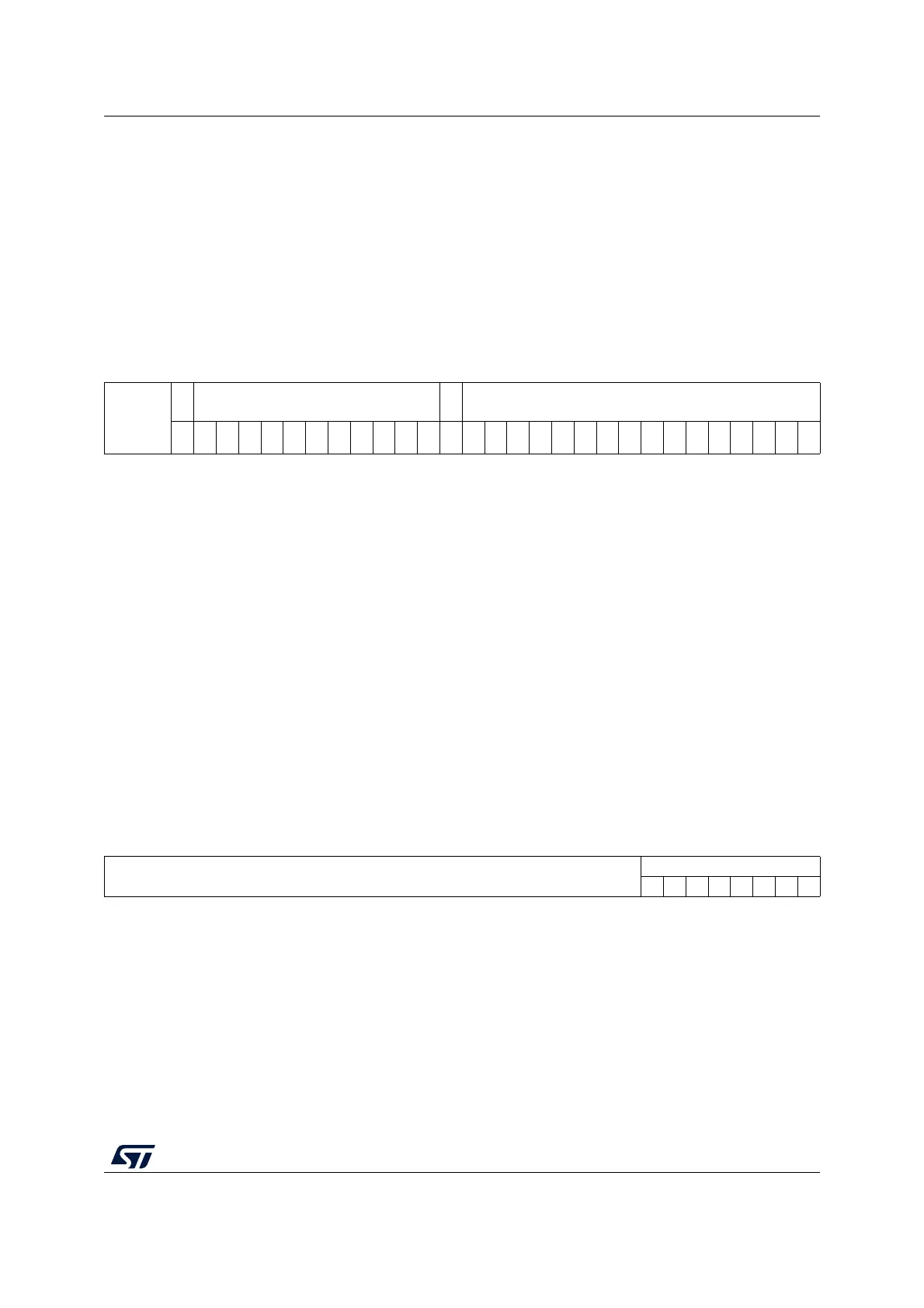

Ethernet DMA missed frame and buffer overflow counter register

(ETH_DMAMFBOCR)

Address offset: 0x1020

Reset value: 0x0000 0000

The DMA maintains two counters to track the number of missed frames during reception.

This register reports the current value of the counter. The counter is used for diagnostic

purposes. Bits [15:0] indicate missed frames due to the STM32F20x and STM32F21x buffer

being unavailable (no receive descriptor was available). Bits [27:17] indicate missed frames

due to Rx FIFO overflow conditions and runt frames (good frames of less than 64 bytes).

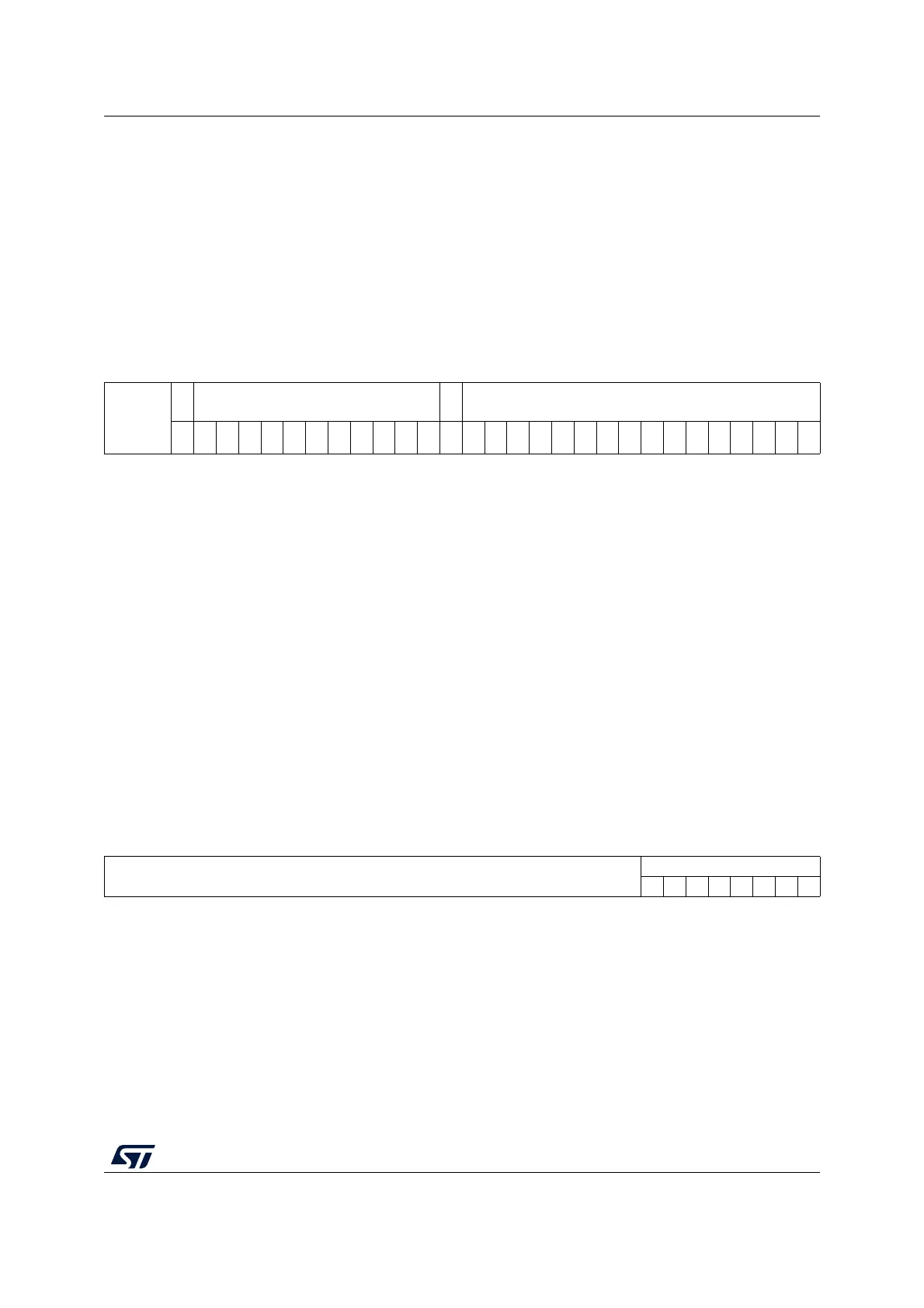

Ethernet DMA receive status watchdog timer register (ETH_DMARSWTR)

Address offset: 0x1024

Reset value: 0x0000 0000

This register, when written with a non-zero value, enables the watchdog timer for the receive

status (RS, ETH_DMASR[6]).

313029282726252423222120191817161514131211109876543210

Reserved

OFOC

MFA

OMFC

MFC

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

rc_

r

Bits 31:29 Reserved, must be kept at reset value.

Bit 28 OFOC: Overflow bit for FIFO overflow counter

Bits 27:17 MFA: Missed frames by the application

Indicates the number of frames missed by the application

Bit 16 OMFC: Overflow bit for missed frame counter

Bits 15:0 MFC: Missed frames by the controller

Indicates the number of frames missed by the Controller due to the host receive buffer being

unavailable. This counter is incremented each time the DMA discards an incoming frame.

313029282726252423222120191817161514131211109876543210

Reserved

RSWTC

rw rw rw rw rw rw rw rw

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 RSWTC: Receive status (RS) watchdog timer count

Indicates the number of HCLK clock cycles multiplied by 256 for which the watchdog timer

is set. The watchdog timer gets triggered with the programmed value after the RxDMA

completes the transfer of a frame for which the RS status bit is not set due to the setting of

RDES1[31] in the corresponding descriptor. When the watchdog timer runs out, the RS bit

is set and the timer is stopped. The watchdog timer is reset when the RS bit is set high due

to automatic setting of RS as per RDES1[31] of any received frame.

Loading...

Loading...