RM0033 Rev 9 1151/1381

RM0033 USB on-the-go high-speed (OTG_HS)

1260

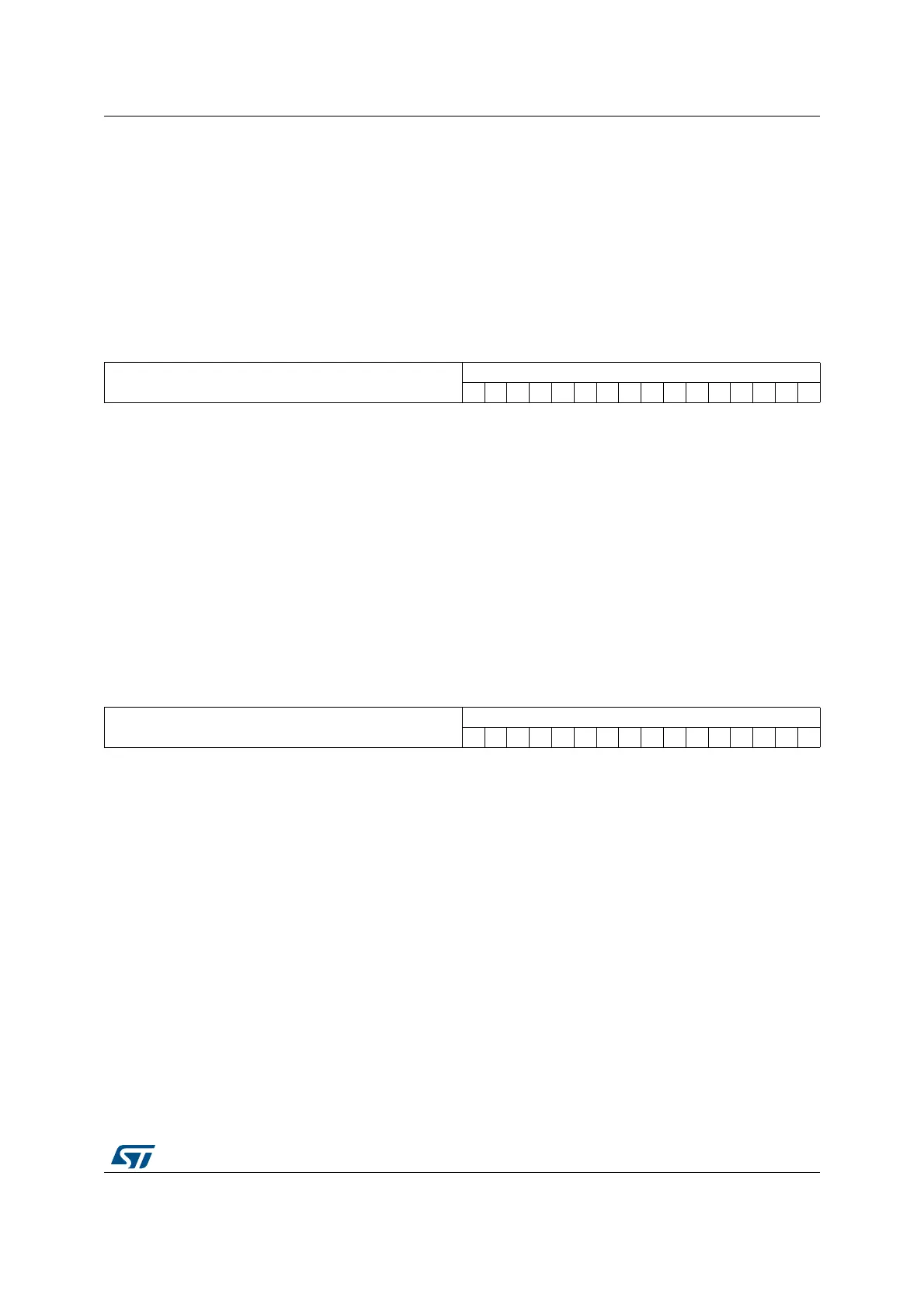

OTG_HS Host all channels interrupt register (OTG_HS_HAINT)

Address offset: 0x414

Reset value: 0x0000 000

When a significant event occurs on a channel, the host all channels interrupt register

interrupts the application using the host channels interrupt bit of the Core interrupt register

(HCINT bit in OTG_HS_GINTSTS). This is shown in Figure 377. There is one interrupt bit

per channel, up to a maximum of 16 bits. Bits in this register are set and cleared when the

application sets and clears bits in the corresponding host channel-x interrupt register.

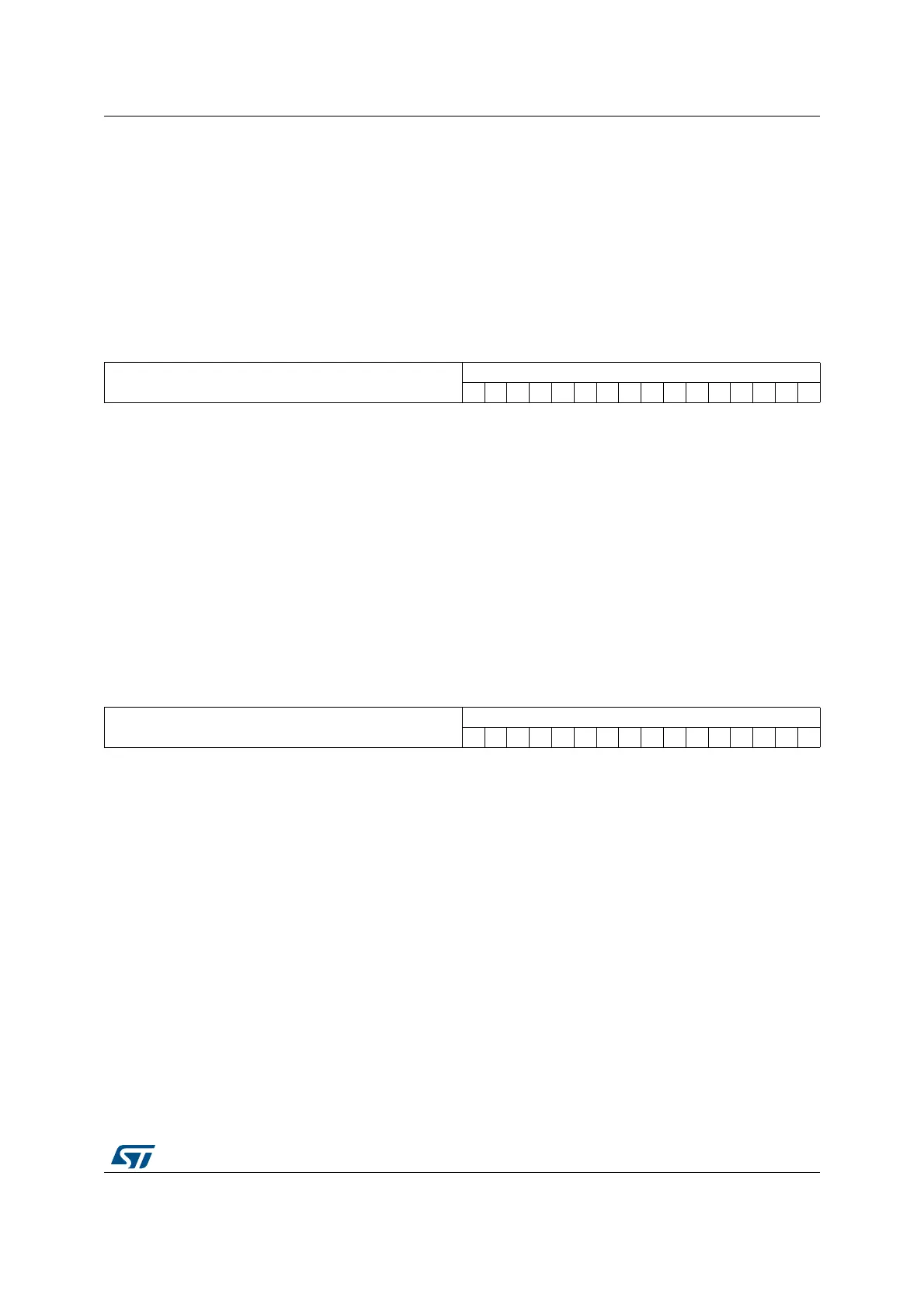

OTG_HS host all channels interrupt mask register (OTG_HS_HAINTMSK)

Address offset: 0x418

Reset value: 0x0000 0000

The host all channel interrupt mask register works with the host all channel interrupt register

to interrupt the application when an event occurs on a channel. There is one interrupt mask

bit per channel, up to a maximum of 16 bits.

313029282726252423222120191817161514131211109876543210

Reserved

HAINT

rrrrrrrrrrrrrrrr

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 HAINT: Channel interrupts

One bit per channel: Bit 0 for Channel 0, bit 15 for Channel 15

313029282726252423222120191817161514131211109876543210

Reserved

HAINTM

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 Reserved, must be kept at reset value.

Bits 15:0 HAINTM: Channel interrupt mask

0: Masked interrupt

1: Unmasked interrupt

One bit per channel: Bit 0 for channel 0, bit 15 for channel 15

Loading...

Loading...