Ethernet (ETH): media access control (MAC) with DMA controller RM0033

922/1381 RM0033 Rev 9

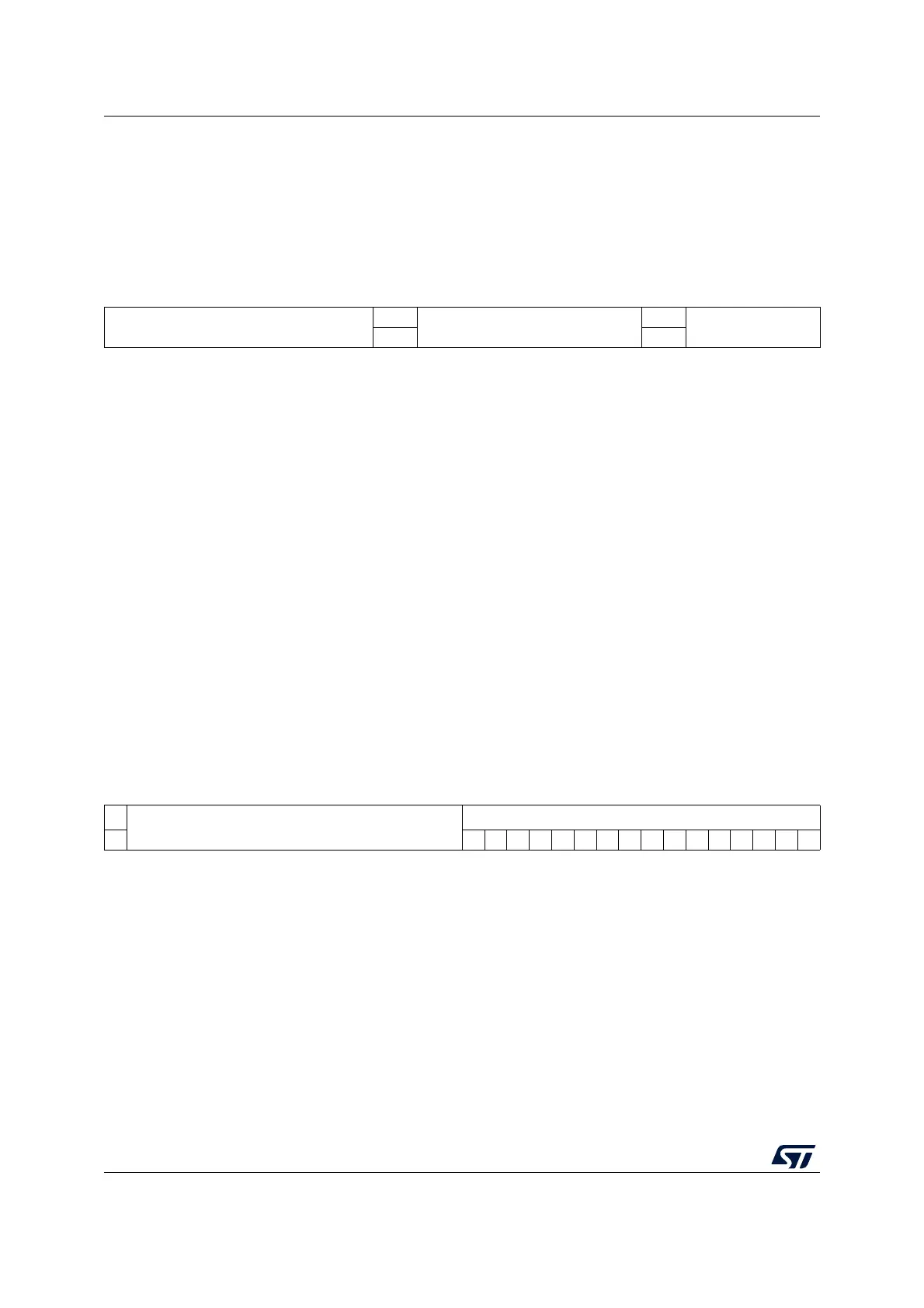

Ethernet MAC interrupt mask register (ETH_MACIMR)

Address offset: 0x003C

Reset value: 0x0000 0000

The ETH_MACIMR register bits make it possible to mask the interrupt signal due to the

corresponding event in the ETH_MACSR register.

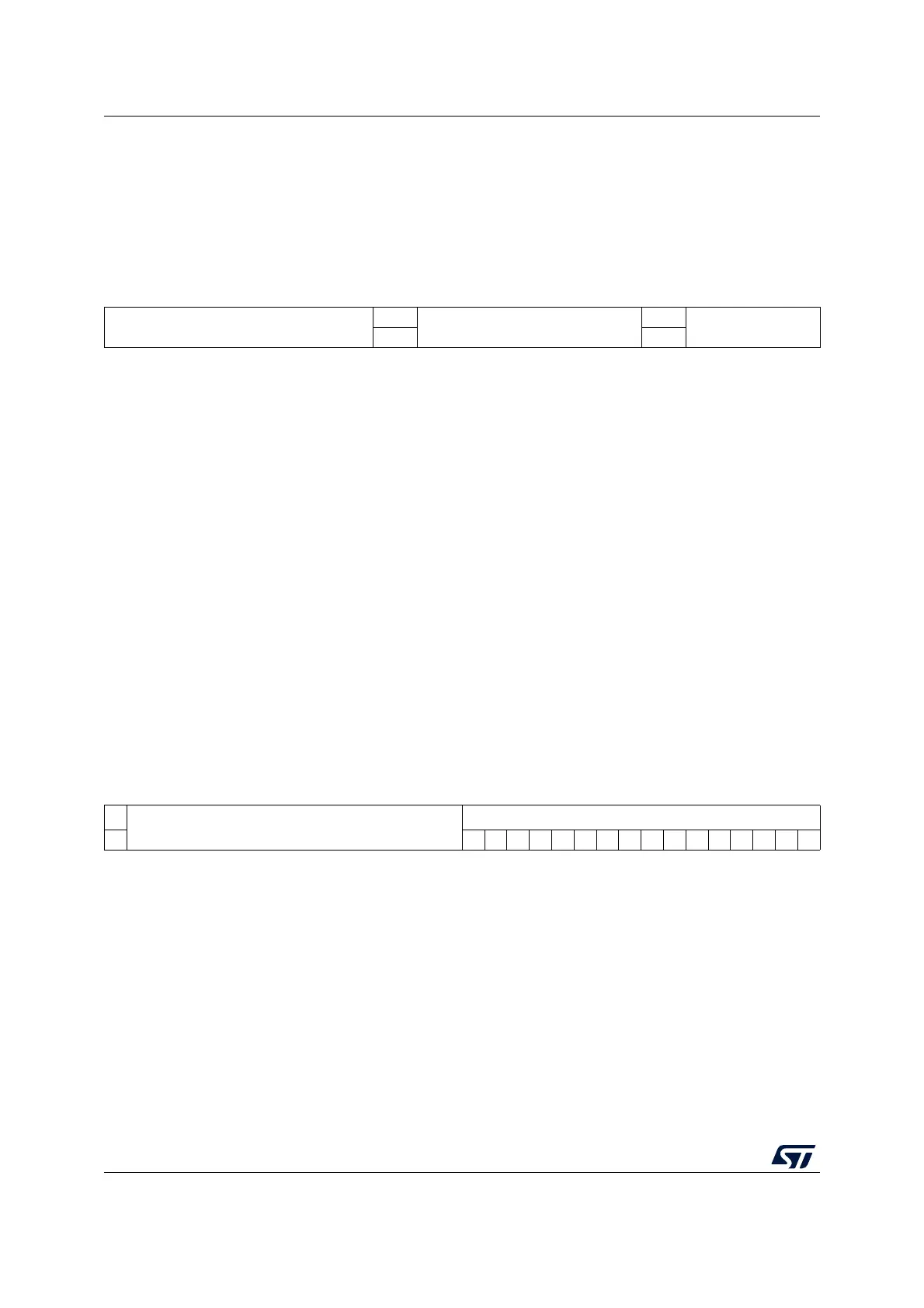

Ethernet MAC address 0 high register (ETH_MACA0HR)

Address offset: 0x0040

Reset value: 0x8000 FFFF

The MAC address 0 high register holds the upper 16 bits of the 6-byte first MAC address of

the station. Note that the first DA byte that is received on the MII interface corresponds to

the LS Byte (bits [7:0]) of the MAC address low register. For example, if 0x1122 3344 5566

is received (0x11 is the first byte) on the MII as the destination address, then the MAC

address 0 register [47:0] is compared with 0x6655 4433 2211.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

TSTIM

Reserved

PMTIM

Reserved

rw rw

Bits 15:10 Reserved, must be kept at reset value.

Bit 9 TSTIM: Time stamp trigger interrupt mask

When set, this bit disables the time stamp interrupt generation.

Bits 8:4 Reserved, must be kept at reset value.

Bit 3 PMTIM: PMT interrupt mask

When set, this bit disables the assertion of the interrupt signal due to the setting of the PMT

Status bit in ETH_MACSR.

Bits 2:0 Reserved, must be kept at reset value.

313029282726252423222120191817161514131211109876543210

MO

Reserved

MACA0H

1 rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 MO: Always 1.

Bits 30:16 Reserved, must be kept at reset value.

Bits 15:0 MACA0H: MAC address0 high [47:32]

This field contains the upper 16 bits (47:32) of the 6-byte MAC address0. This is used by the

MAC for filtering for received frames and for inserting the MAC address in the transmit flow

control (Pause) frames.

Loading...

Loading...