RM0033 Rev 9 923/1381

RM0033 Ethernet (ETH): media access control (MAC) with DMA controller

956

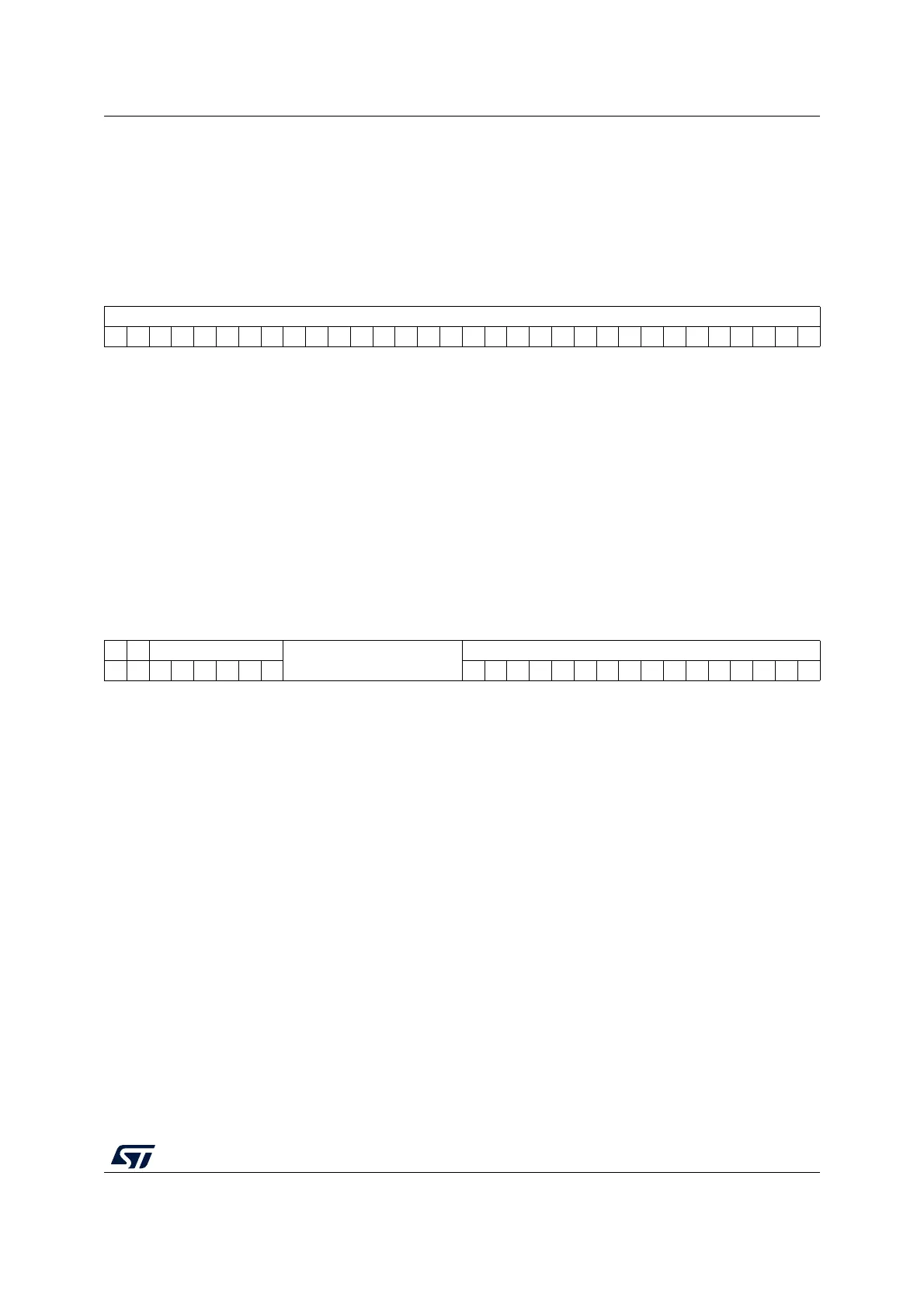

Ethernet MAC address 0 low register (ETH_MACA0LR)

Address offset: 0x0044

Reset value: 0xFFFF FFFF

The MAC address 0 low register holds the lower 32 bits of the 6-byte first MAC address of

the station.

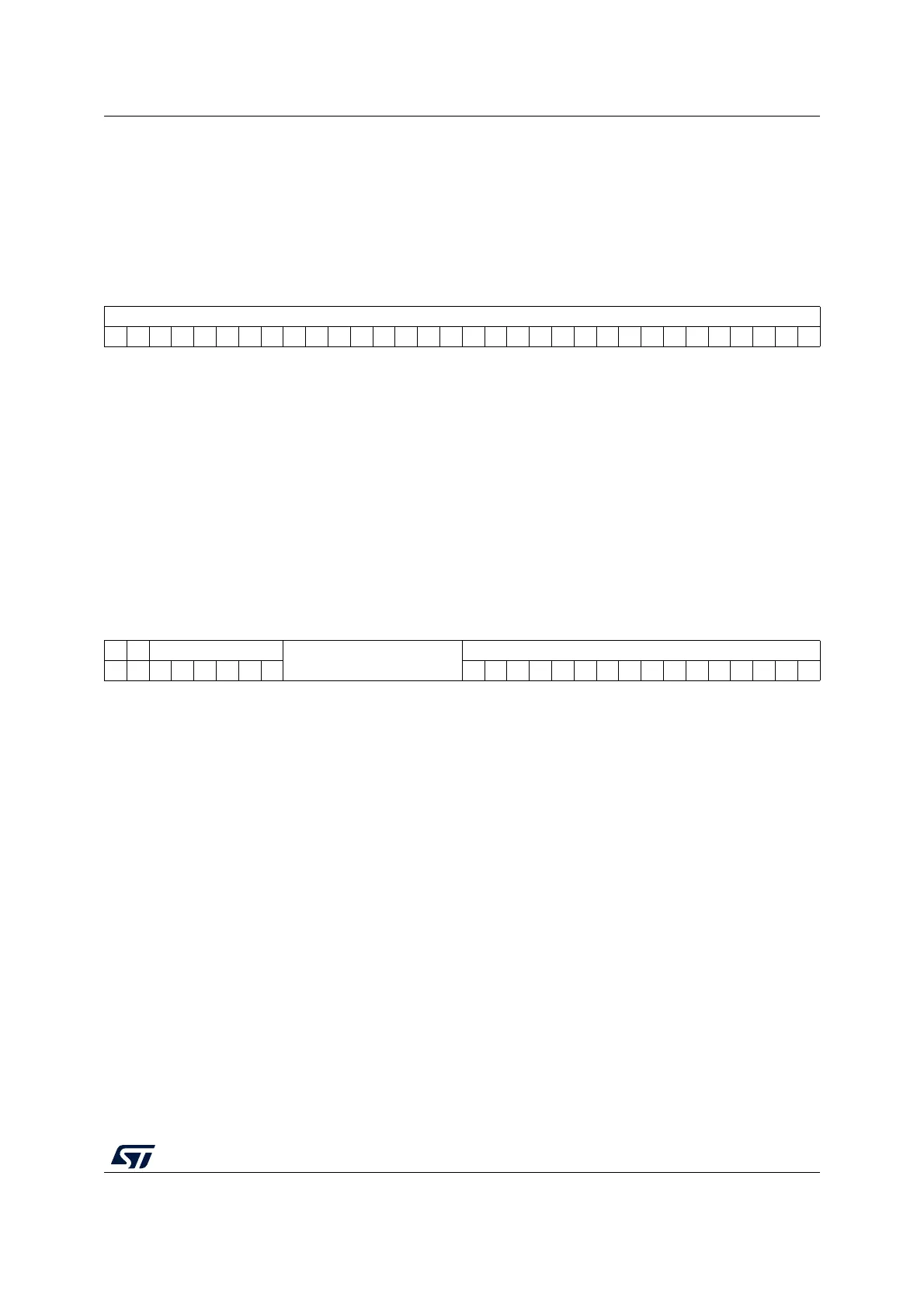

Ethernet MAC address 1 high register (ETH_MACA1HR)

Address offset: 0x0048

Reset value: 0x0000 FFFF

The MAC address 1 high register holds the upper 16 bits of the 6-byte second MAC address

of the station.

313029282726252423222120191817161514131211109876543210

MACA0L

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 MACA0L: MAC address0 low [31:0]

This field contains the lower 32 bits of the 6-byte MAC address0. This is used by the MAC

for filtering for received frames and for inserting the MAC address in the transmit flow control

(Pause) frames.

313029282726252423222120191817161514131211109876543210

AE SA MBC

Reserved

MACA1H

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bit 31 AE: Address enable

When this bit is set, the address filters use the MAC address1 for perfect filtering. When this

bit is cleared, the address filters ignore the address for filtering.

Bit 30 SA: Source address

When this bit is set, the MAC address1[47:0] is used for comparison with the SA fields of the

received frame.

When this bit is cleared, the MAC address1[47:0] is used for comparison with the DA fields

of the received frame.

Bits 29:24 MBC: Mask byte control

These bits are mask control bits for comparison of each of the MAC address1 bytes. When

they are set high, the MAC core does not compare the corresponding byte of received

DA/SA with the contents of the MAC address1 registers. Each bit controls the masking of the

bytes as follows:

– Bit 29: ETH_MACA1HR [15:8]

– Bit 28: ETH_MACA1HR [7:0]

– Bit 27: ETH_MACA1LR [31:24]

…

– Bit 24: ETH_MACA1LR [7:0]

Loading...

Loading...