TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Information

V1.0 2013-07

User Manual (Volume 2) 1-4

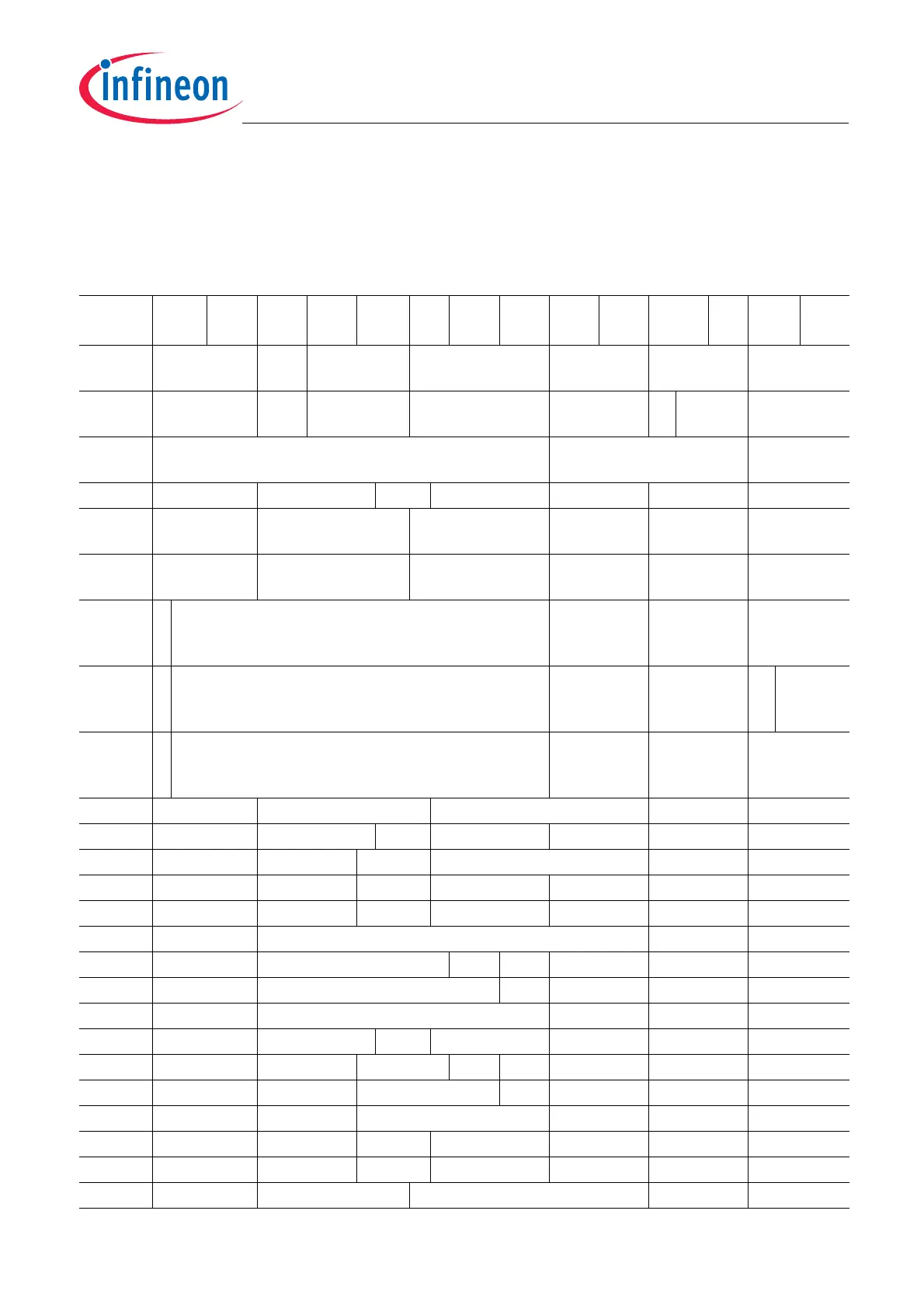

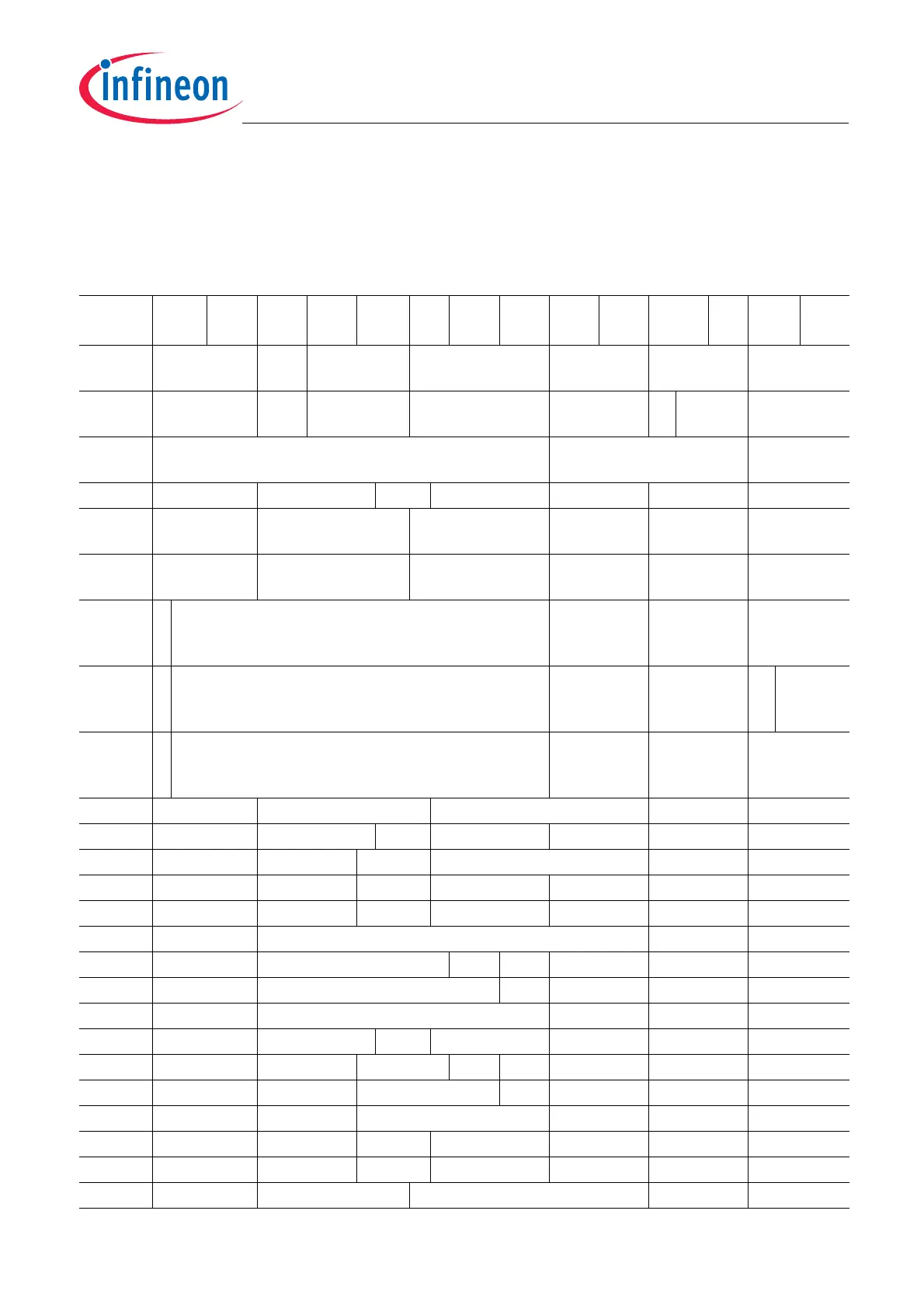

1.2.2 32-bit Opcode Formats

Note:Bit[0] of the op1 field is always 1 for 32-bit instructions.

Table 1-6 32-bit Opcode Formats

31:30

29:28

27:26

25:24

23:22

21:20

21:20

19:18

17:16

15:14

13:12

11:10

9-8

7-6

5-0

ABS off18

[9:6]

op2 off18

[13:10] off18[5:0]

off18

[17:14]

s1/d

op1

ABSB off18

[9:6]

op2 off18

[13:10] off18[5:0]

off18

[17:14]

b bpos3

op1

B disp24[15:0] disp24[23:16]

op1

BIT d pos2 op2 pos1 s2 s1 op1

BO off10[9:6] op2 off10[5:0] s2 s1/d

op1

BOL off16[9:6] off16[15:10] off16[5:0] s2 s1/d

op1

BRC o

p

2

disp15 const4 s1

op1

BRN o

p

2

disp15 n[3:0] s1

n[4]

op1

BRR o

p

2

disp15 s2 s1 op1

RC d op2 const9 s1 op1

RCPW d pos op2 width const4 s1 op1

RCR d s3 op2 const9 s1 op1

RCRR d s3 op2 - const4 s1 op1

RCRW d s3 op2 width const4 s1 op1

RLC d const16 s1 op1

RR d op2 - n s2 s1 op1

RR1 d op2 n s2 s1 op1

RR2 d op2 s2 s1 op1

RRPW d pos op2 width s2 s1 op1

RRR d s3 op2 - n s2 s1 op1

RRR1 d s3 op2 n s2 s1 op1

RRR2 d s3 op2 s2 s1 op1

RRRR d s3 op2 - s2 s1 op1

RRRW d s3 op2 width s2 s1 op1

SYS - op2 - s1/d op1

Loading...

Loading...