TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-20

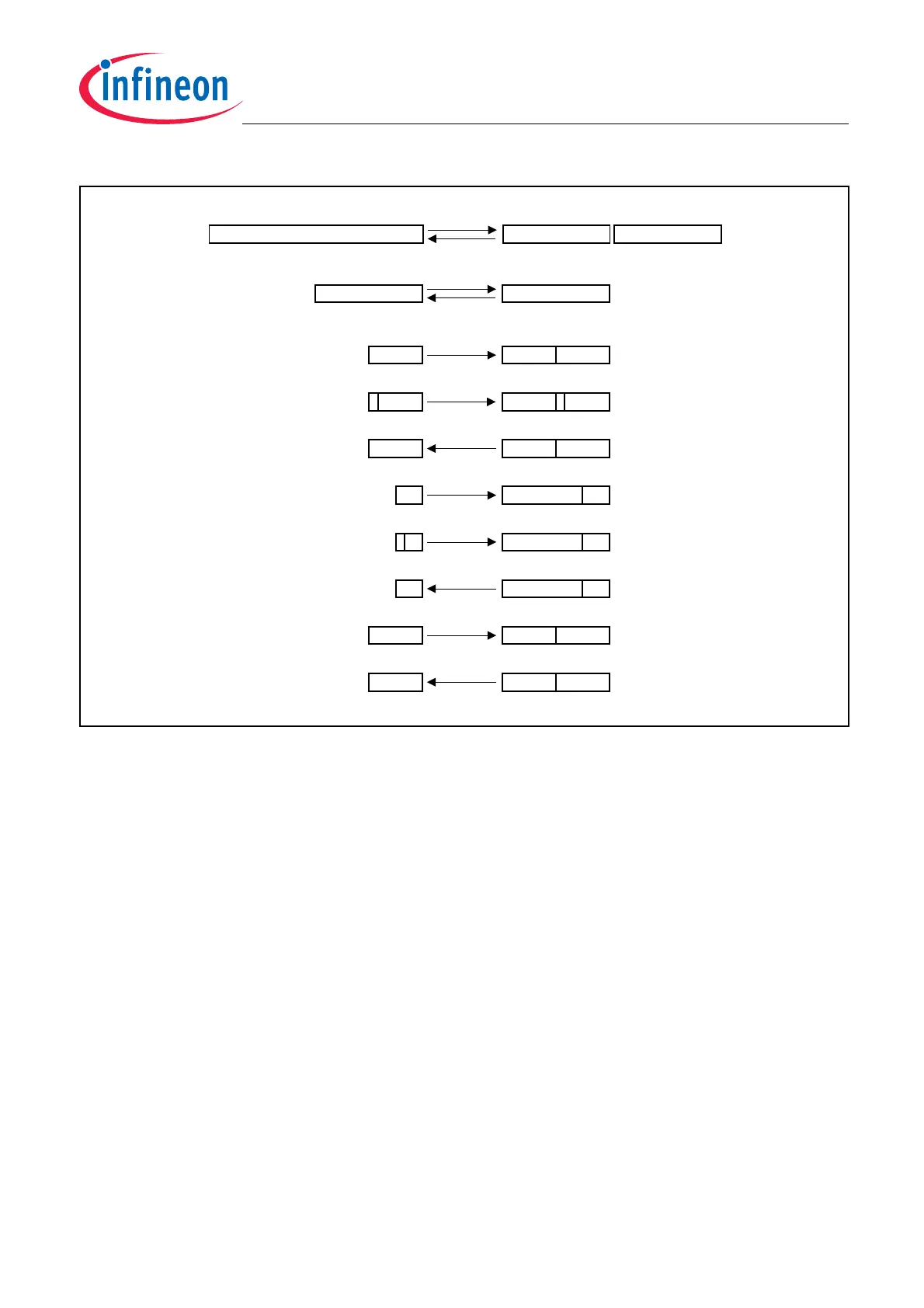

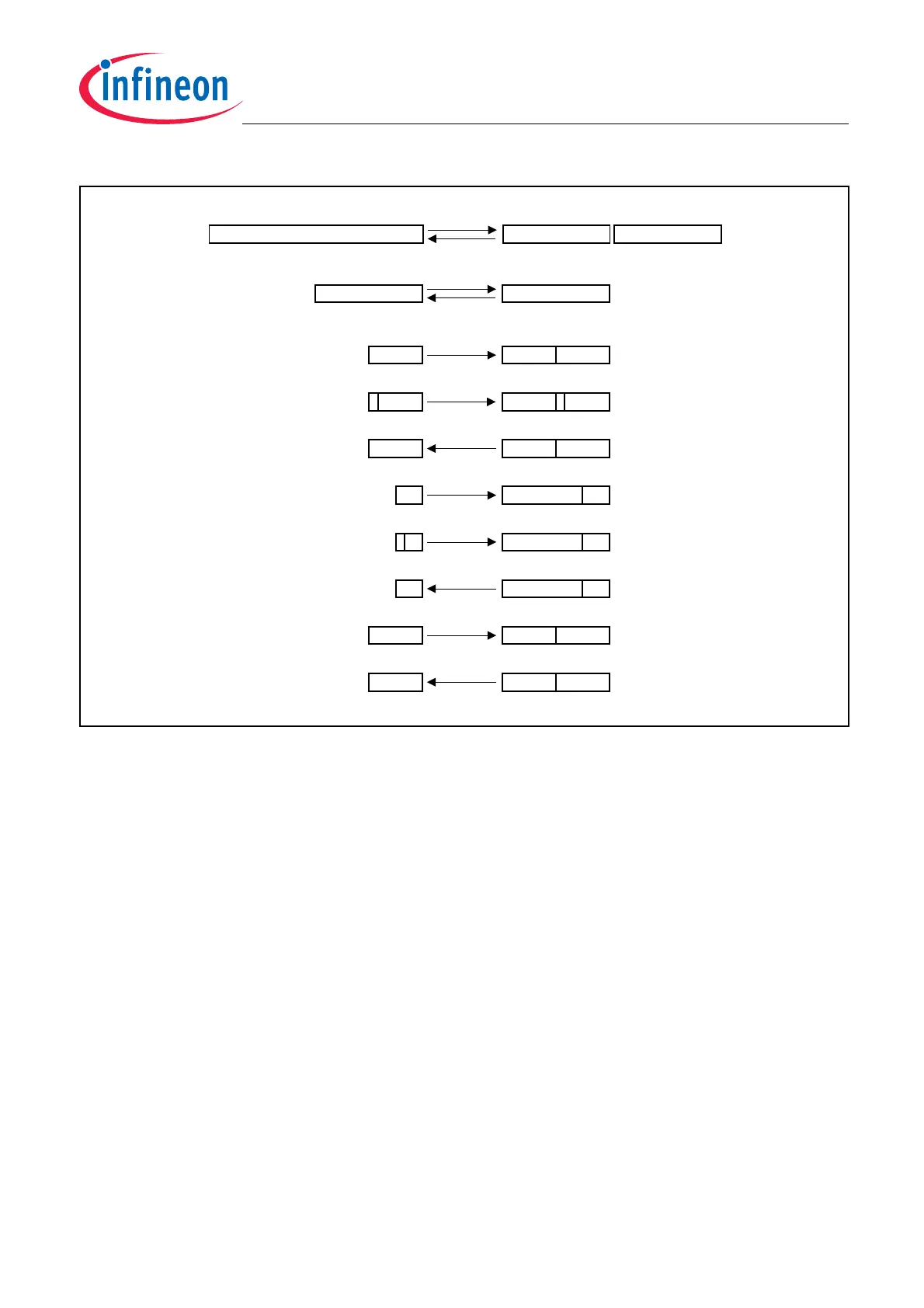

Figure 2-17 Load/Store Basic Data Type

2.10.2 Load Bit

The approaches for loading individual bits depend on whether the bit within the word (or byte) is given statically or

dynamically.

Loading a single bit with a fixed bit offset from a byte pointer is accomplished with an ordinary load instruction. It

is then possible to extract, logically operate on, or jump to any bit in a register.

Loading a single bit with a variable bit offset from a word-aligned byte pointer, is performed with a special scaled

offset instruction. This offset instruction shifts the bit offset to the right by three positions (producing a byte offset),

adds this result to the byte pointer above, and finally zeros out the two lower bits, so aligning the access on a word

boundary.

A word load can then access the word that contains the bit, which can be extracted with an extract instruction that

only uses the lower five bits of the bit pointer; i.e. the bits that were either shifted out or masked out above. For

example:

ADDSC.AT A8, A9, D8; // A9 = byte pointer. D8 = bit offset

LD.W D9, [A8]

EXTR.U D10, D9, D8, 1; // D10[0] = loaded bit

2.10.3 Store Bit and Bit Field

The ST.T (Store Bit) instruction can clear or set single memory or peripheral bits, resulting in reduced code size.

ST.T specifies a byte address and a bit number within that byte, and indicates whether the bit should be set or

cleared. The addressable range for ST.T is the first 16-KBytes of each of the 16 memory segments.

TC1060B

m1

015

m1

07

m1

015

m1

07

s

m1

07

m1

015

m1

015

s

m1

015

m1

031

m1

063

Memory Data

LD.W / LD.A

m1

031

ST.W / ST.A

LD.D / LD.DA

ST.D / ST.DA

M1[63:32]

031

M1[31:0]

031

D[n+1] / A[n+1] D[n] / A[n]

D[n]

0

31

m1

01516

zero fill

LD.HU

s

31 16

sign fill

LD.H

m1

015

s

D[n]

ST.H

D[n]

x

31

m1

01516

0

31

zero fill

0

D[n]

m1

87

LD.BU

s

31

sign fill

0

D[n]

m1

87

LD.B

x

31 0

D[n]

m1

87

ST.B

LD.Q

D[n]

0

31

m1

01516

zero fill

ST.Q

D[n]

x

31

m1

01516

Registers

D[n] / A[n]

Loading...

Loading...