TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-381

SWAPMSK.W

Swap under Mask

Description

The SWAPMSK.W instruction enables individual bits or bytes to be used as semaphore. Up to 32 semaphores

(bits) can be tested in parallel.

SWAPMSK.W uses an Extended register to provide both mask and swap data. It swaps through a mask the

contents of E[a][31:0] with the contents of the memory word specified by the addressing mode. Only those bits are

swapped where the corresponding bits in the mask E[a][63:32] are set. Register D[a] is unconditionally updated

with the contents of the memory word specified by the addressing mode.

SWAPMSK.WA[b], off10, E[a] (BO)(Base + Short Offset Addressing Mode)

EA = A[b] + sign_ext(off10);

tmp = M(EA, word);

M(EA, word) = (tmp & ~D[a+1]) | (D[a] & D[a+1]);

D[a] = tmp;

SWAPMSK.WP[b], E[a] (BO)(Bit-reverse Addressing Mode)

index = zero_ext(A[b+1][15:0]);

incr = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

tmp = M(EA, word);

M(EA, word) = (tmp & ~D[a+1]) | (D[a] & D[a+1]);

D[a] = tmp;

new_index = reverse16(reverse16(index) + reverse16(incr));

A[b+1] = {incr[15:0], new_index[15:0]};

SWAPMSK.WP[b], off10, E[a] (BO)(Circular Addressing Mode)

index = zero_ext(A[b+1][15:0]);

length = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

tmp = M(EA, word);

M(EA, word) = (tmp & ~D[a+1]) | (D[a] & D[a+1]);

D[a] = tmp;

new_index = index + sign_ext(off10);

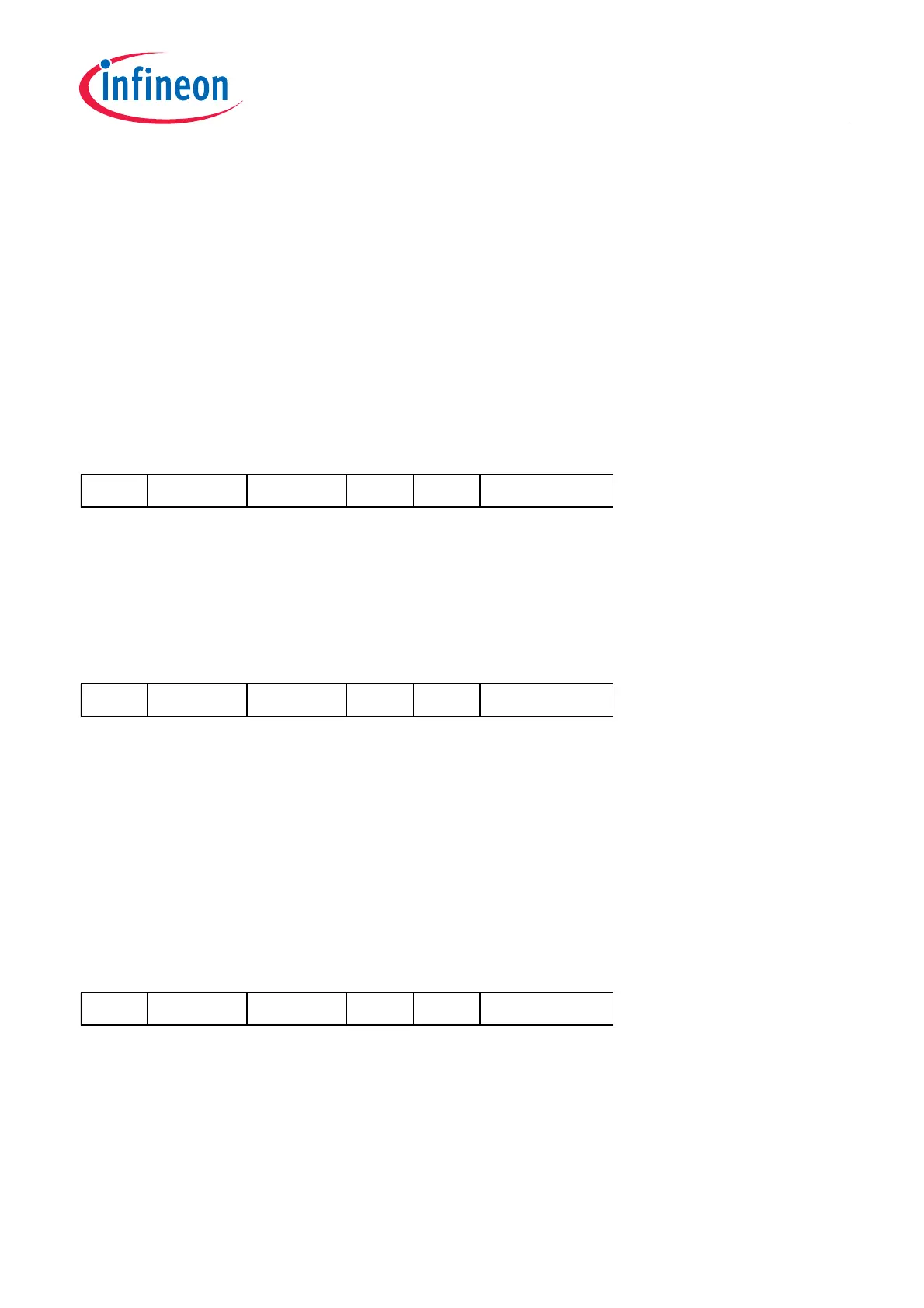

31

off10[9:6]

28 27

22

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

49

H

0

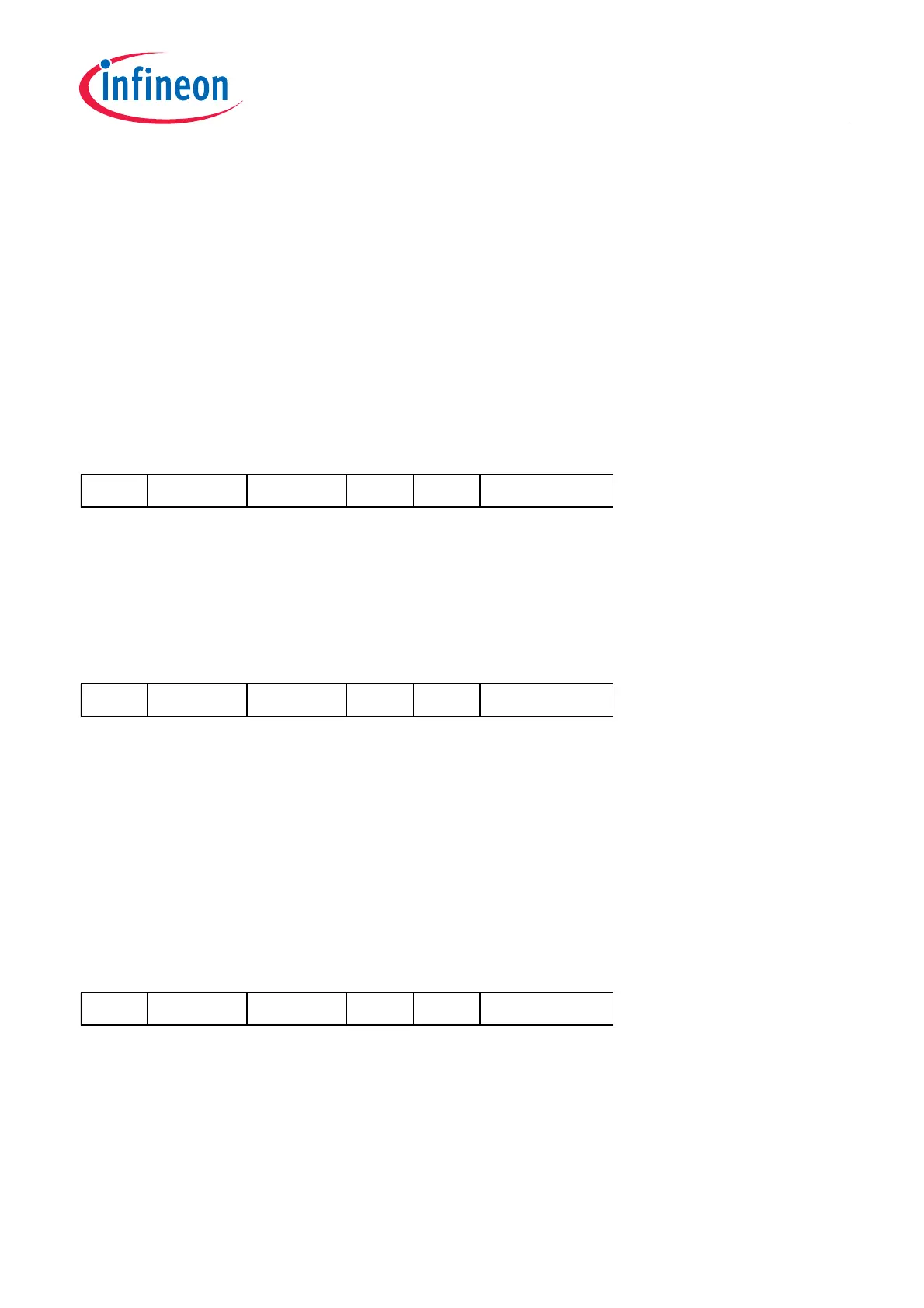

31

-

28 27

02

H

22 21

-

16 15

b

12 11

a

8 7

69

H

0

31

off10[9:6]

28 27

12

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

69

H

0

Loading...

Loading...