TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-322

RSUBS

Reverse-Subtract with Saturation

RSUBS.U

Reverse-Subtract Unsigned with Saturation

Description

Subtract the contents of data register D[a] from the value const9 and put the result in data register D[c]. The

operands are treated as signed (RSUBS) or unsigned (RSUBS.U) 32-bit integers, with saturation on signed

(RSUBS) or unsigned (RSUBS.U) overflow. The value const9 is sign-extended before the operation is performed.

RSUBSD[c], D[a], const9 (RC)

result = sign_ext(const9) - D[a];

D[c] = ssov(result, 32);

RSUBS.UD[c], D[a], const9 (RC)

result = sign_ext(const9) - D[a]; // unsigned

D[c] = suov(result, 32);

Status Flags

Examples

rsubs d3, d1, #126

rsubs.u d3, d1, #126

See Also

RSUB

C Not set by these instructions.

V signed:

overflow = (result > 7FFFFFFF

H

) OR (result < -80000000

H

);

if (overflow) then PSW.V = 1 else PSW.V = 0;

unsigned:

overflow = (result > FFFFFFFF

H

) OR (result < 00000000

H

);

if (overflow) then PSW.V = 1 else PSW.V = 0;

SV if (overflow) then PSW.SV = 1 else PSW.SV = PSW.SV;

AV advanced_overflow = result[31] ^ result[30];

if (advanced_overflow) then PSW.AV = 1 else PSW.AV = 0;

SAV if (advanced_overflow) then PSW.SAV = 1 else PSW.SAV = PSW.SAV;

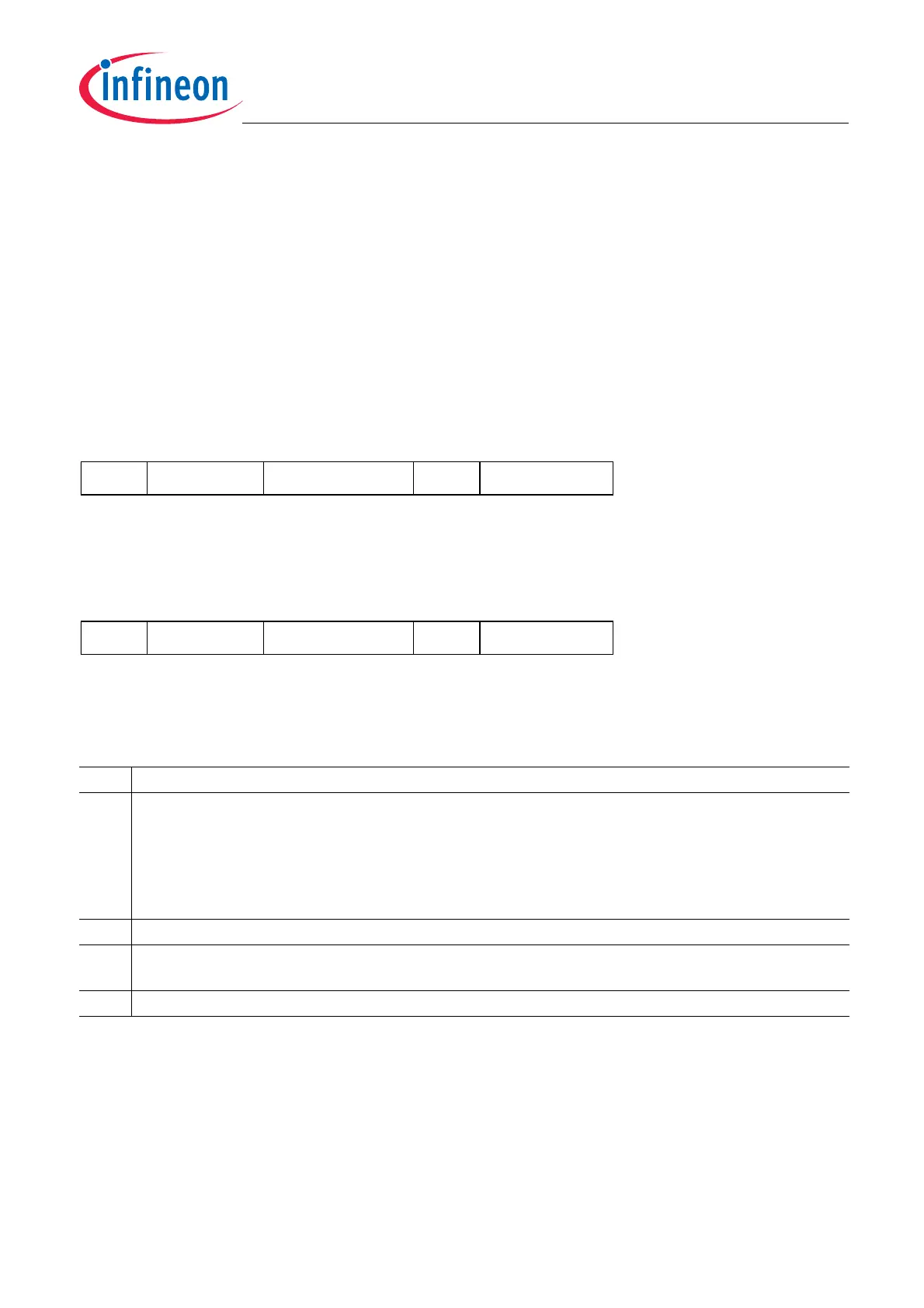

31

c

28 27

0A

H

21 20

const9

12 11

a

8 7

8B

H

0

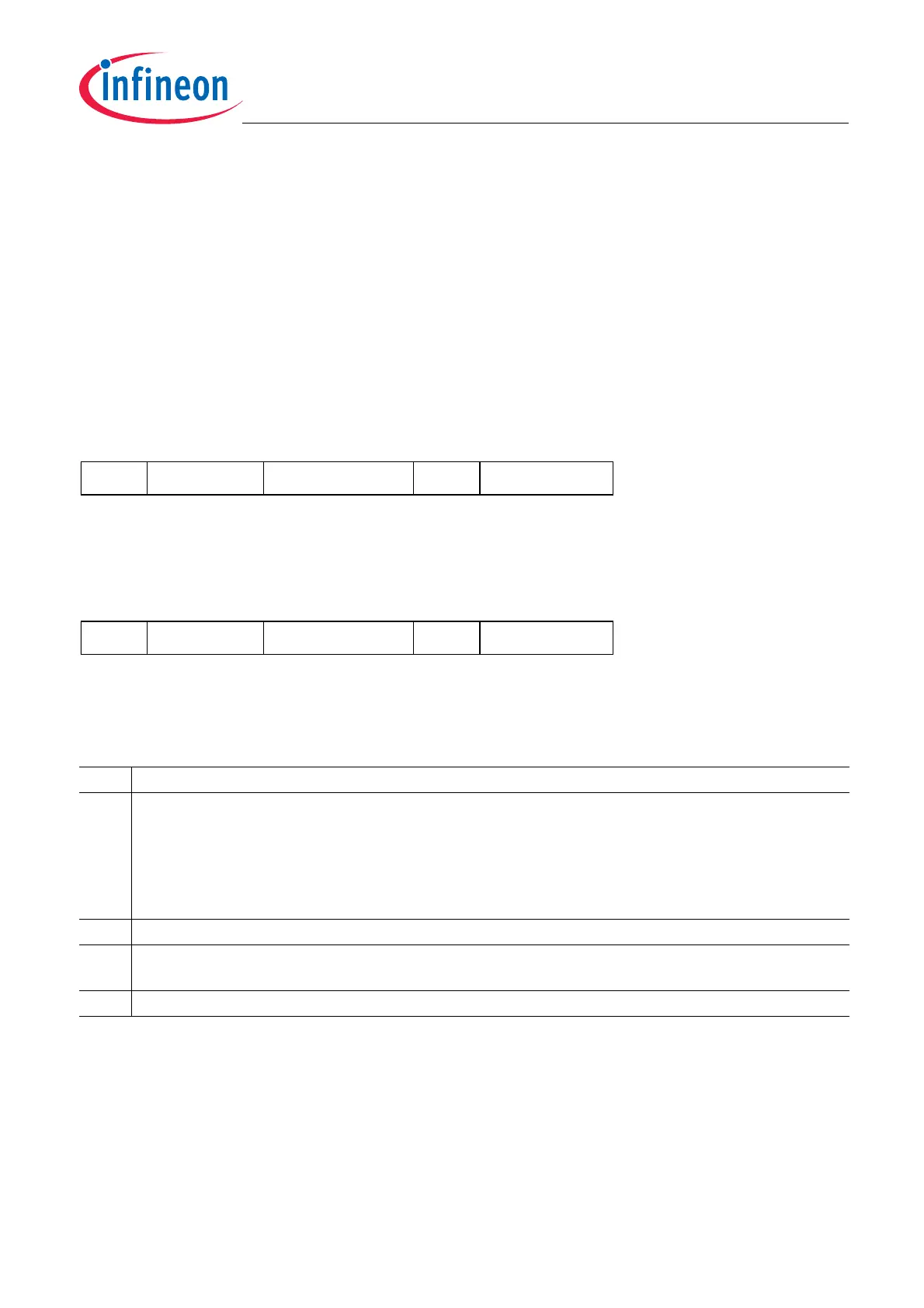

31

c

28 27

0B

H

21 20

const9

12 11

a

8 7

8B

H

0

Loading...

Loading...