TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-236

MSUB

Multiply-Subtract

MSUBS

Multiply-Subtract, Saturated

Description

Multiply two signed 32-bit integers. Subtract the product from a signed 32-bit or 64-bit integer and put the result

into a 32-bit or 64-bit register. The value const9 is sign-extended before the multiplication is performed. The

MSUBS result is saturated on overflow.

MSUBD[c], D[d], D[a], const9 (RCR)

32 - (32 * K9) --> 32 signed

result = D[d] - (D[a] * sign_ext(const9));

D[c] = result[31:0];

MSUBE[c], E[d], D[a], const9 (RCR)

64 - (32 * K9) --> 64 signed

result = E[d] - (D[a] * sign_ext(const9));

E[c] = result[63:0];

MSUBD[c], D[d], D[a], D[b] (RRR2)

32 - (32 * 32) --> 32 signed

result = D[d] - (D[a] * D[b]);

D[c] = result[31:0];

MSUBE[c], E[d], D[a], D[b] (RRR2)

64 - (32 * 32) --> 64 signed

result = E[d] - (D[a] * D[b]);

E[c] = result[63:0];

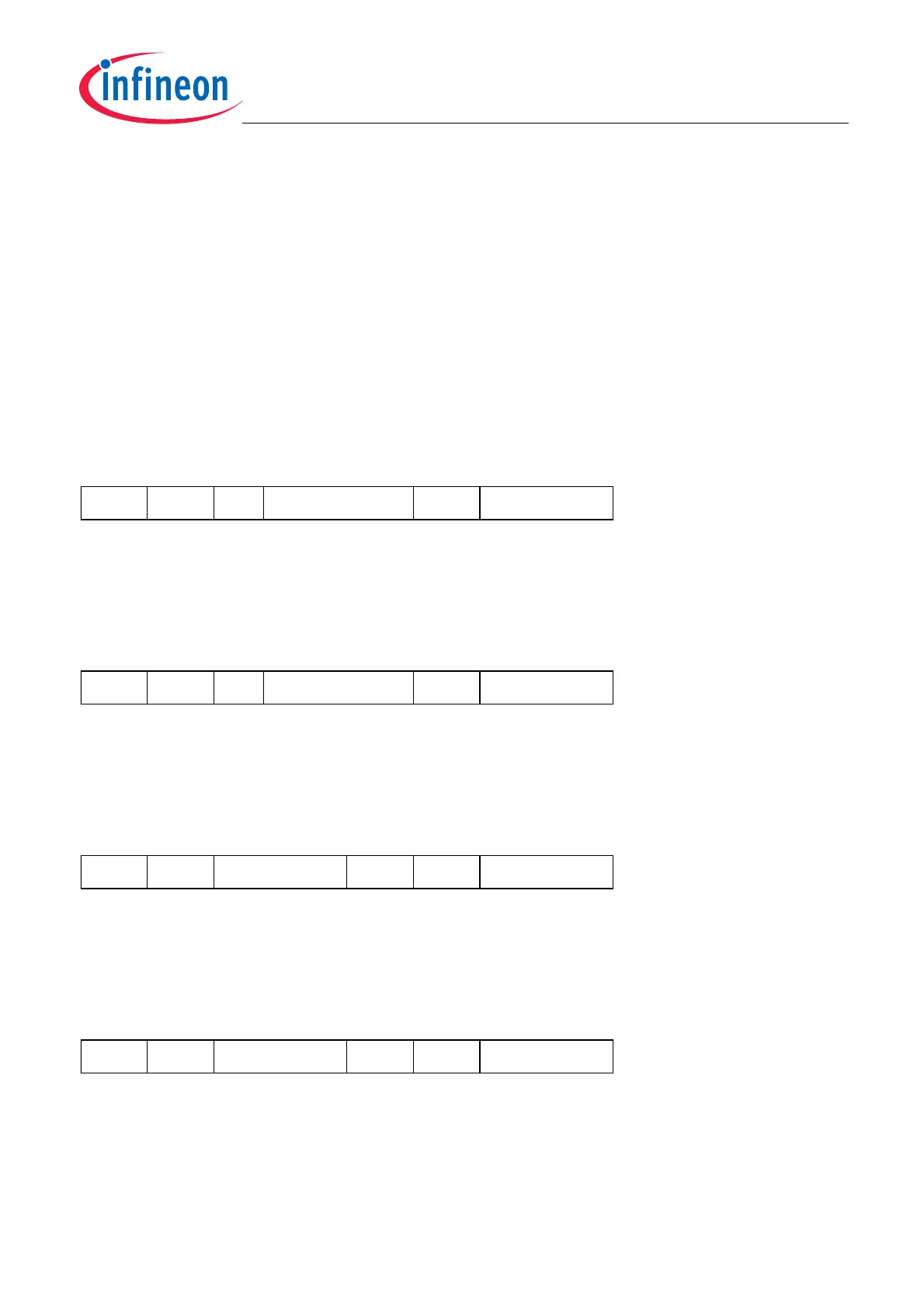

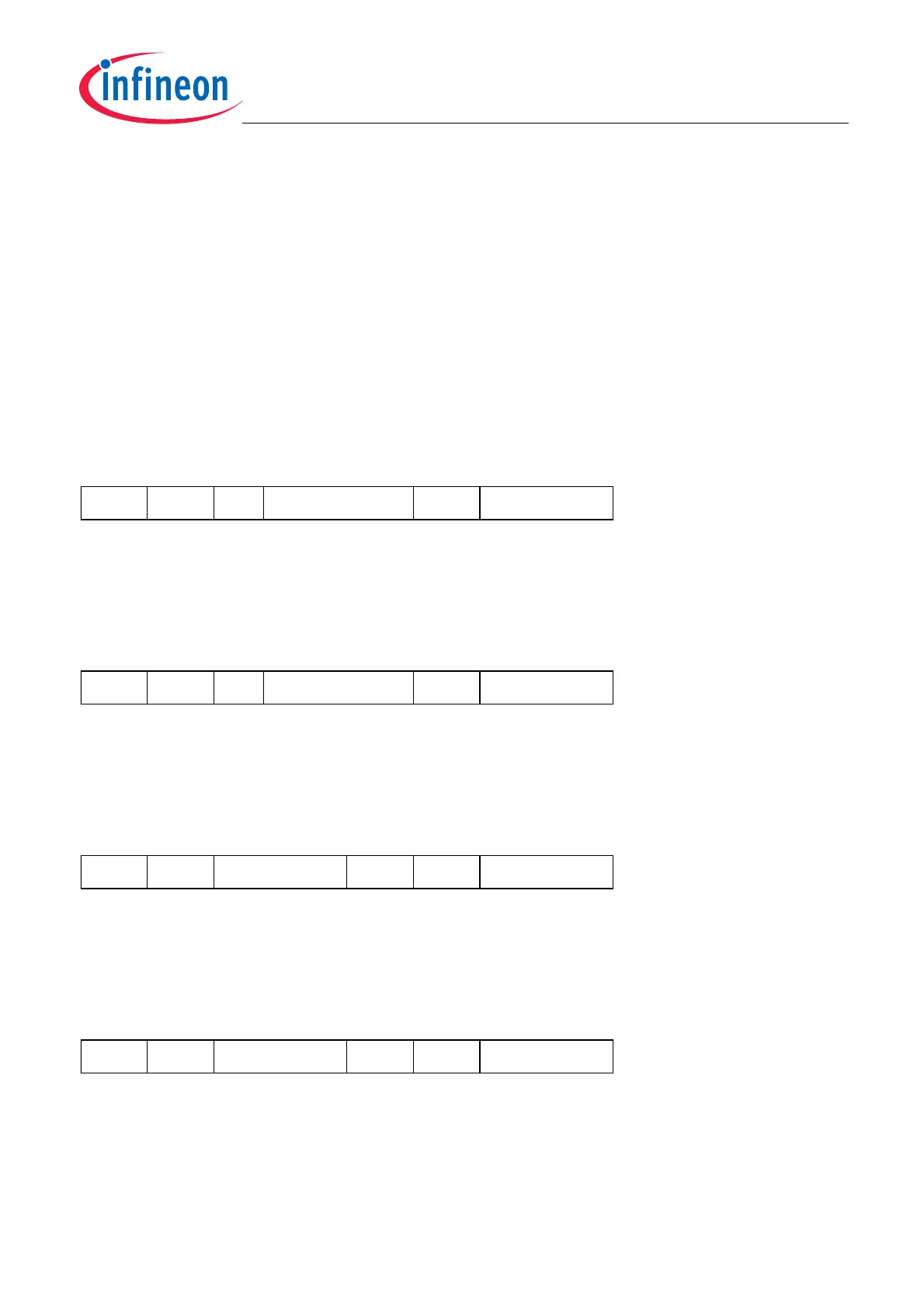

MSUBSD[c], D[d], D[a], const9 (RCR)

32 - (32 * K9) --> 32 signed saturated

31

c

28 27

d

24 23

01

H

21 20

const9

12 11

a

8 7

33

H

0

31

c

28 27

d

24 23

03

H

21 20

const9

12 11

a

8 7

33

H

0

31

c

28 27

d

24 23

0A

H

16 15

b

12 11

a

8 7

23

H

0

31

c

28 27

d

24 23

6A

H

16 15

b

12 11

a

8 7

23

H

0

Loading...

Loading...