TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-82

DEXTR

Extract from Double Register

Description

Extract 32-bits from registers {D[a], D[b]}, where D[a] contains the most-significant 32-bits of the value, starting at

the bit number specified by either 32 - D[d][4:0] (instruction format RRRR) or 32 - pos (instruction format RRPW).

Put the result in D[c].

Note:D[a] and D[b] can be any two data registers or the same register. For this instruction they are treated as a

64-bit entity where D[a] contributes the high order bits and D[b] the low order bits.

DEXTRD[c], D[a], D[b], pos (RRPW)

D[c] = ({D[a], D[b]} << pos)[63:32];

DEXTRD[c], D[a], D[b], D[d] (RRRR)

D[c] = ({D[a], D[b]} << D[d][4:0])[63:32];

If D[d] > 31 the result is undefined.

Status Flags

Examples

dextr d1, d3, d5, d7

dextr d1, d3, d5, #11

See Also

EXTR, EXTR.U, INSERT, INS.T, INSN.T

C Not set by this instruction.

V Not set by this instruction.

SV Not set by this instruction.

AV Not set by this instruction.

SAV Not set by this instruction.

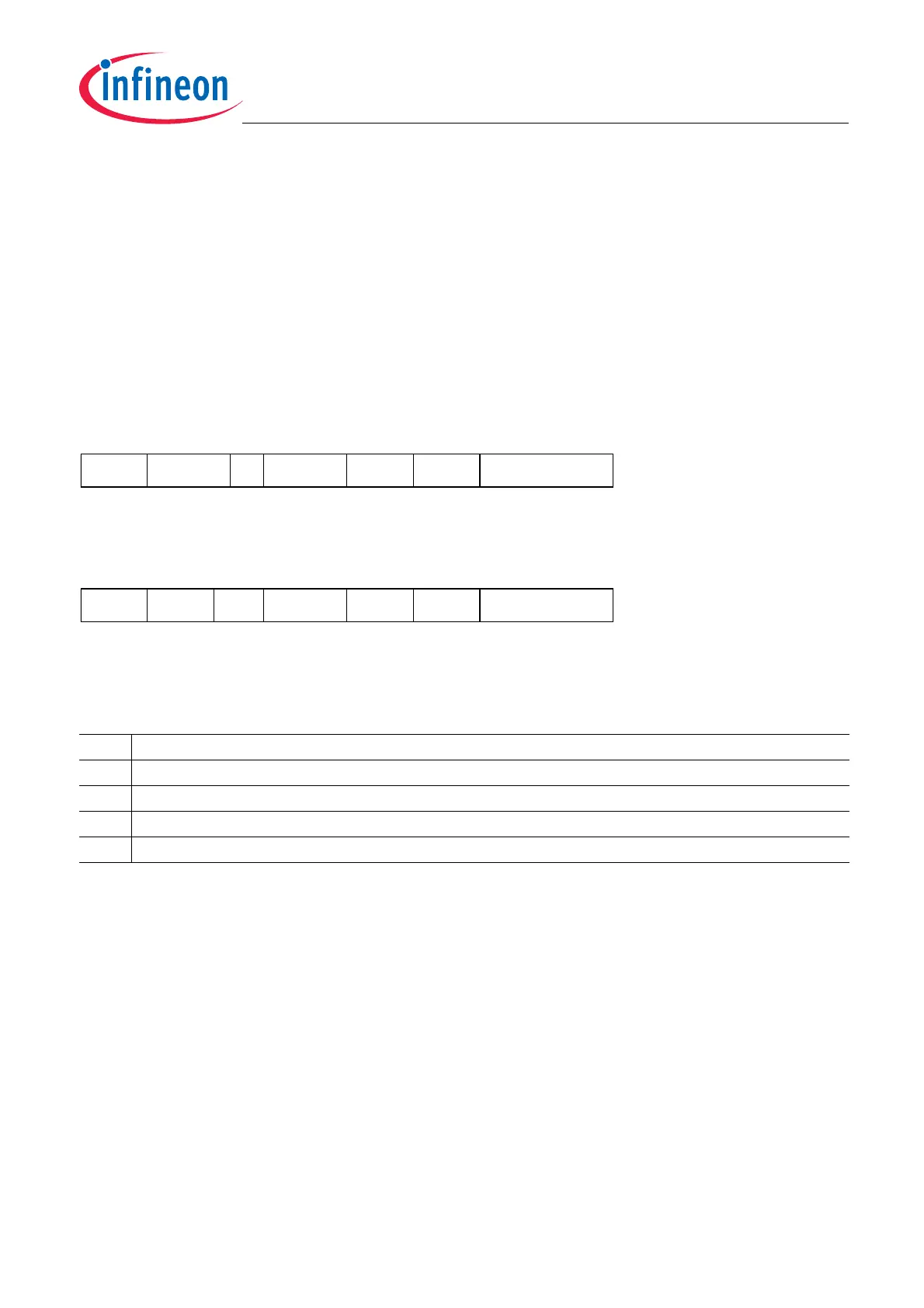

31

c

28 27

pos

23 22

00

H

21 20

-

16 15

b

12 11

a

8 7

77

H

0

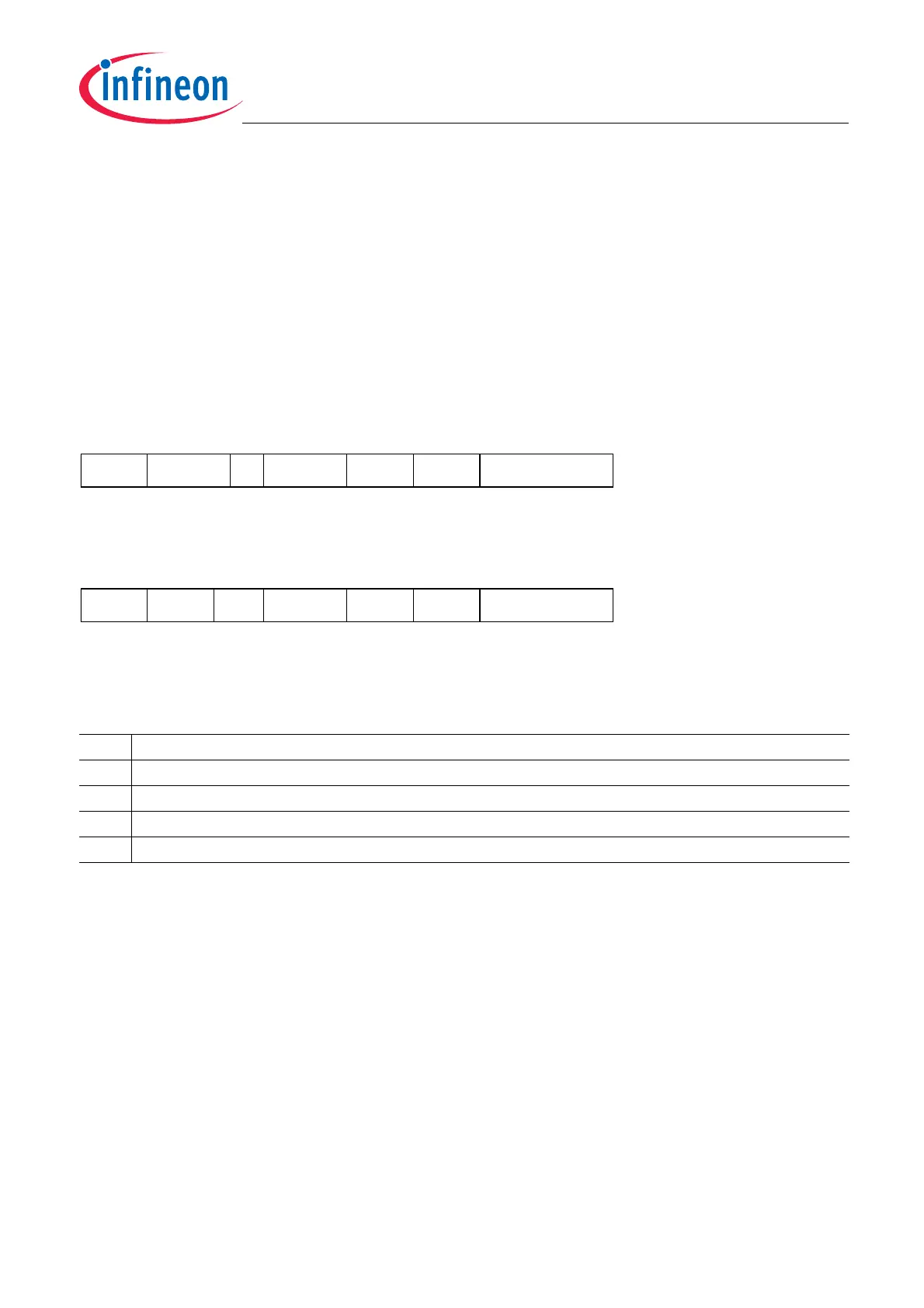

31

c

28 27

d

24 23

04

H

21 20

-

16 15

b

12 11

a

8 7

17

H

0

Loading...

Loading...