TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-17

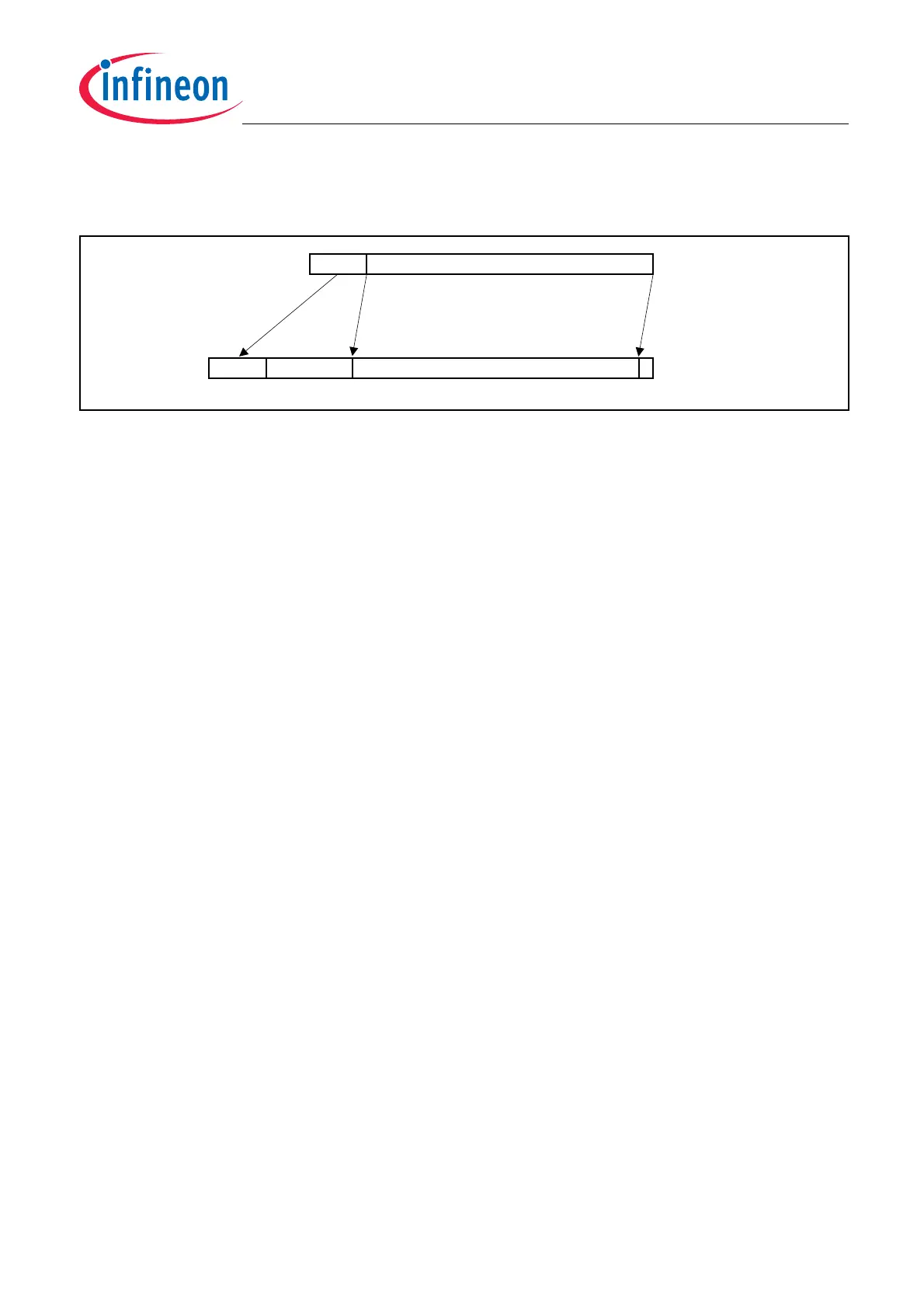

Both the 24-bit and 8-bit relative displacements are scaled by two before they are used, because all instructions

must be aligned on an even address. The use of a 24-bit field as an absolute address is shown in Figure 2-16.

Figure 2-16 Calculation of Absolute Address

2.9.2 Conditional Branch

The conditional branch instructions use the relative addressing mode, with a displacement value encoded in 4, 8

or 15-bits.

The displacement is scaled by 2 before it is used, because all instructions must be aligned on an even address.

The scaled displacement is sign-extended to 32-bits before it is added to the program counter, unless otherwise

noted.

Conditional Jumps on Data Registers

Six of the conditional jump instructions use a 15-bit signed displacement field:

• JEQ (Comparison for Equality)

• JNE (Non-Equality)

• JLT (Less Than)

• JLT.U (Less Than Unsigned)

• JGE (Greater Than or Equal)

• JGE.U (Greater Than or Equal Unsigned)

The second operand to be compared may be an 8-bit sign or zero-extended constant. There are two 16-bit

instructions that test whether the implicit D[15] register is equal to zero (JZ) or not equal to zero (JNZ). The

displacement is 8-bit in this case.

The 16-bit instructions JEQ and JNE compare the implicit D[15] register with a 4-bit, sign-extended constant. The

jump displacement field is limited to a constant for these two instructions.

There is a full set of 16-bit instructions that compare a data register to zero; JZ, JNZ, JLTZ, JLEZ, JGTZ, and

JGEZ.

Because any data register may be specified, the jump displacement is limited to a 4-bit zero-extended constant in

this case.

Conditional Jumps on Address Registers

The conditional jump instructions that use address registers are a subset of the data register conditional jump

instructions. Four conditional jump instructions use a 15-bit signed displacement field:

• JEQ.A (Comparison for Equality)

• JNE.A (Non-Equality)

• JZ.A (Equal to Zero)

• JNZ.A (Non-Equal to Zero)

Because testing pointers for equality to zero is so frequent, two 16-bit instructions, JZ.A and JNZ.A, are provided,

with a displacement field limited to a 4-bit zero extended constant.

TC1059B

2019

0

20

0

24 bit field

from

Absolute

instruction

0

Address

23

21

0000000

2728

31

1

Loading...

Loading...