TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-6

INSERT

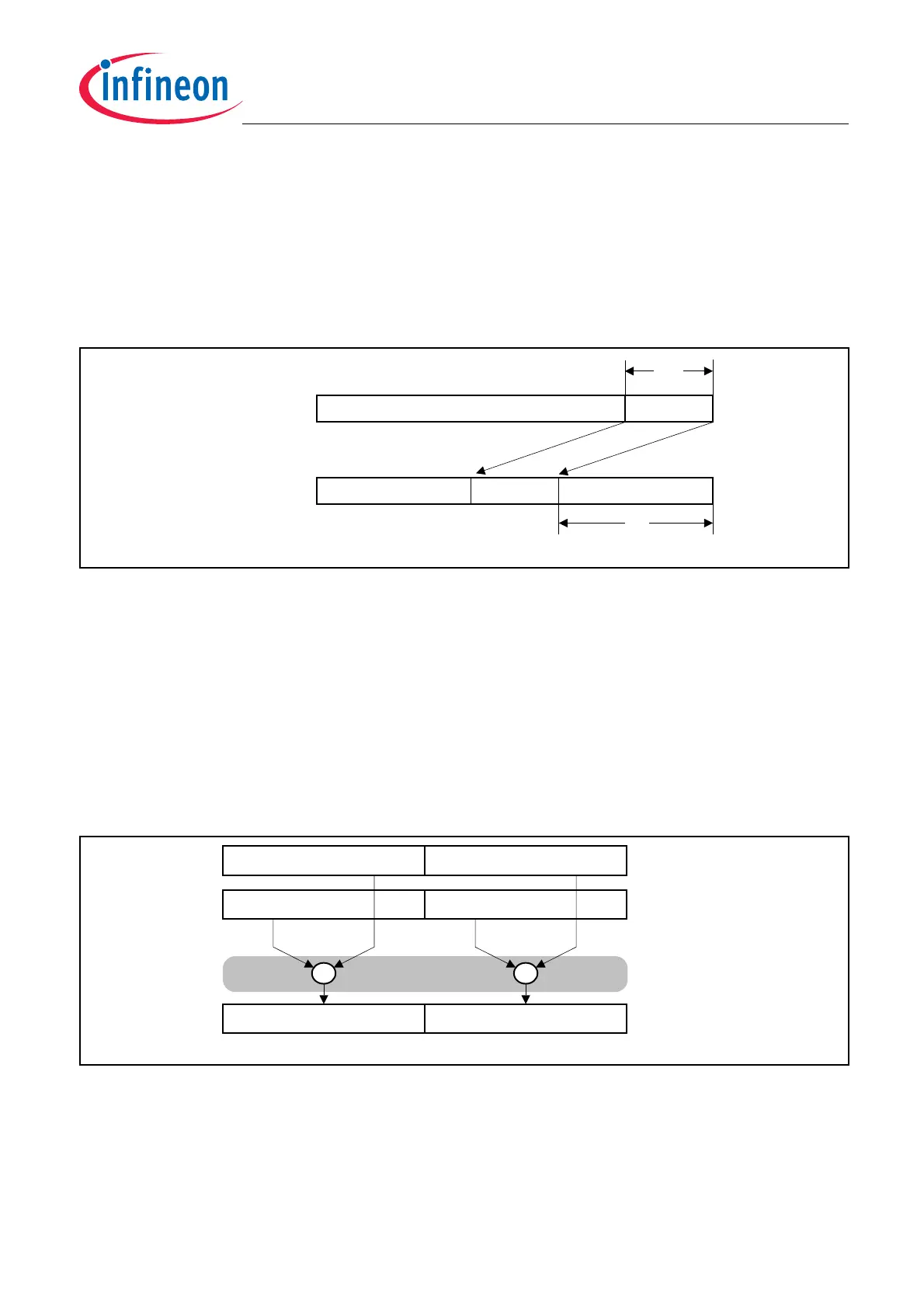

The INSERT instruction takes the width least-significant bits of a source data register, shifted left by pos bits and

substitutes them into the value of another source register. All other (32-w) bits of the value of the second register

are passed through. The width and pos can be specified by two immediate values, by an immediate value and a

data register, or by a data register pair.

There is also an alternative form of INSERT that allows a zero-extended 4-bit constant to be the value which is

inserted.

Figure 2-5 INSERT Operation

2.2 Packed Arithmetic

The packed arithmetic instructions partition a 32-bit word into several identical objects which can then be fetched,

stored, and operated on in parallel. These instructions in particular allow the full exploitation of the 32-bit word of

the TriCore architecture in signal and data processing applications.

The TriCore architecture supports two packed formats:

• Packed Half-word Data format

• Packed Byte Data format

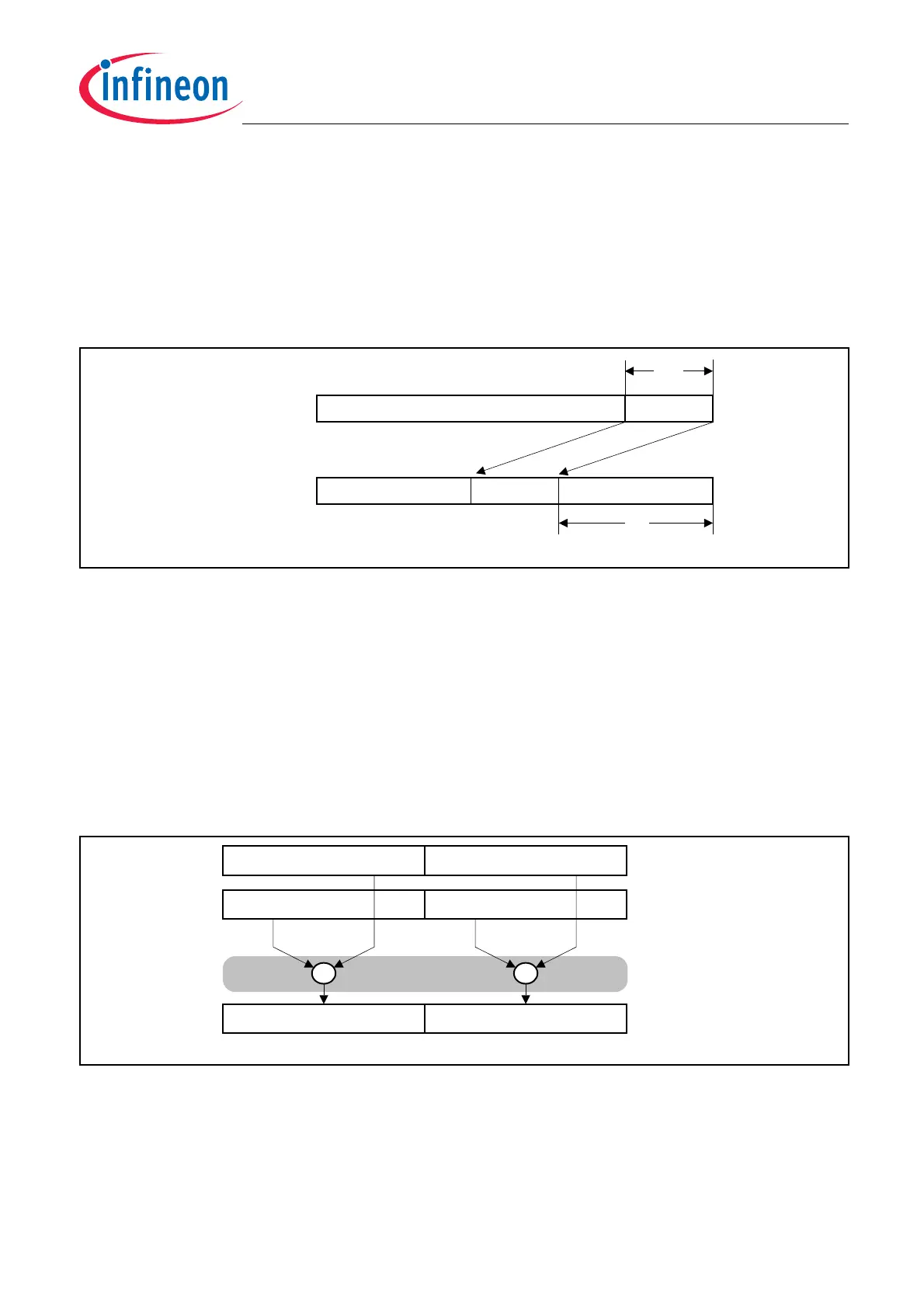

The Packed Half-word Data format divides the 32-bit word into two, 16-bit (half-word) values. Instructions which

operate on data in this way are denoted in the instruction mnemonic by the .H and .HU modifiers.

Figure 2-6 Packed Half-word Data Format

The Packed Byte Data format divides the 32-bit word into four, 8-bit values. Instructions which operate on the data

in this way are denoted by the .B and .BU data type modifiers.

TC1048B

Source Register

31 0

Destination Register

31

0

Pos

Width

TC1049B

Operand m

Operand n

Result

Operation

Half-word 1 Half-word 0

Half-word 1 Half-word 0

Destination 1 Destination 0

Loading...

Loading...