TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-161

LD.H

Load Half-word

LD.HU

Load Half-word Unsigned

Description

Load the half-word contents of the memory location specified by the addressing mode, sign-extended, into data

register D[a].

LD.HD[a], off18 (ABS)(Absolute Addressing Mode)

EA = {off18[17:14], 14b'0, off18[13:0]};

D[a] = sign_ext(M(EA, halfword));

LD.HD[a], A[b], off10 (BO)(Base + Short Offset Addressing Mode)

EA = A[b] + sign_ext(off10);

D[a] = sign_ext(M(EA, halfword));

LD.HD[a], P[b] (BO)(Bit-reverse Addressing Mode)

index = zero_ext(A[b+1][15:0]);

incr = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

D[a] = sign_ext(M(EA, halfword));

new_index = reverse16(reverse16(index) + reverse16(incr));

A[b+1] = {incr[15:0], new_index[15:0]};

LD.HD[a], P[b], off10 (BO)(Circular Addressing Mode)

index = zero_ext(A[b+1][15:0]);

length = zero_ext(A[b+1][31:16]);

EA = A[b] + index;

D[a] = sign_ext(M(EA, halfword));

Load the half-word contents of the memory location specified by the addressing mode, sign-extended, into either

data register D[a] or D[15].

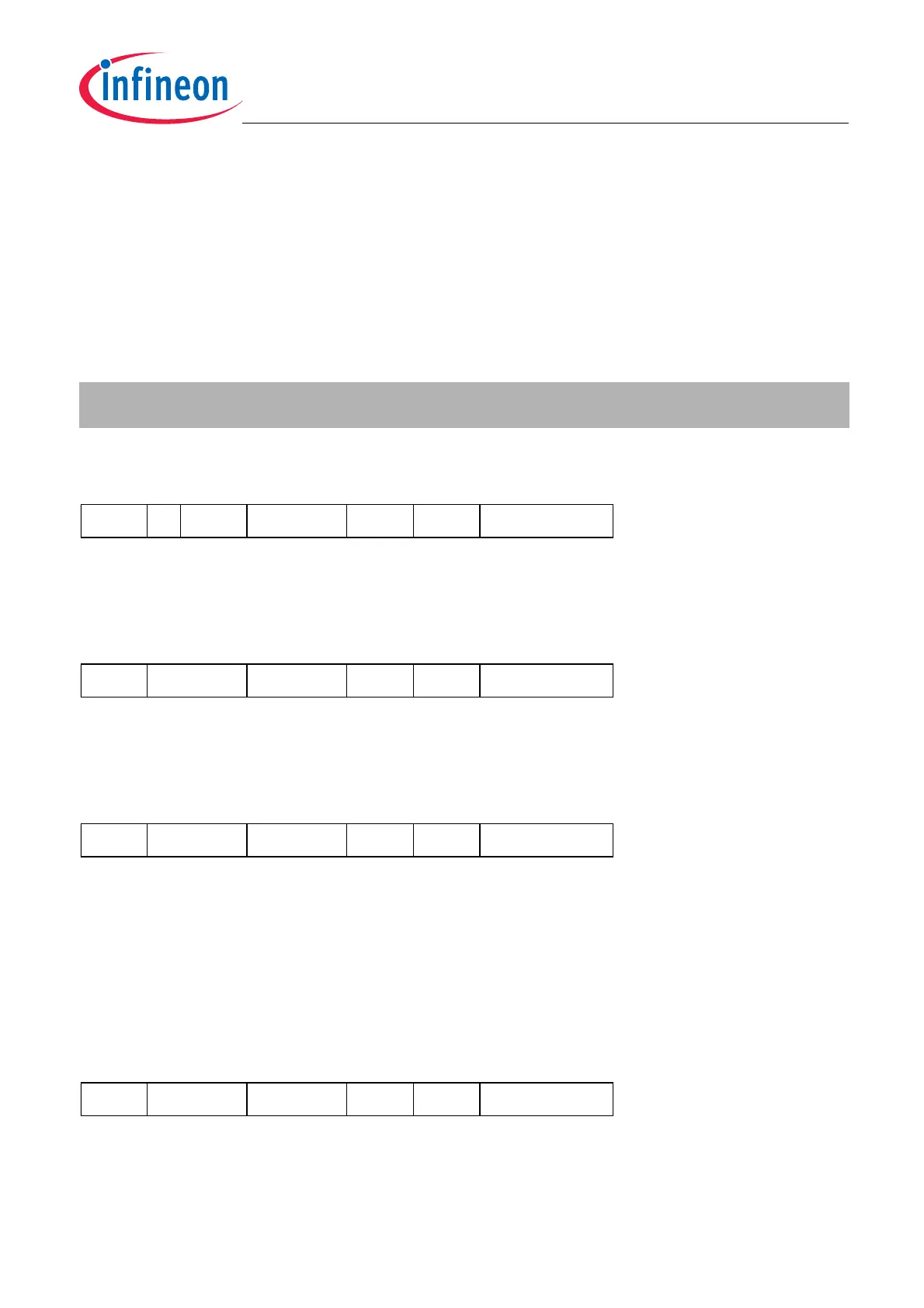

31

off18[9:6]

28 27

02

H

26 25

off18[13:10]

22 21

off18[5:0]

16 15

off18[17:14]

12 11

a

8 7

05

H

0

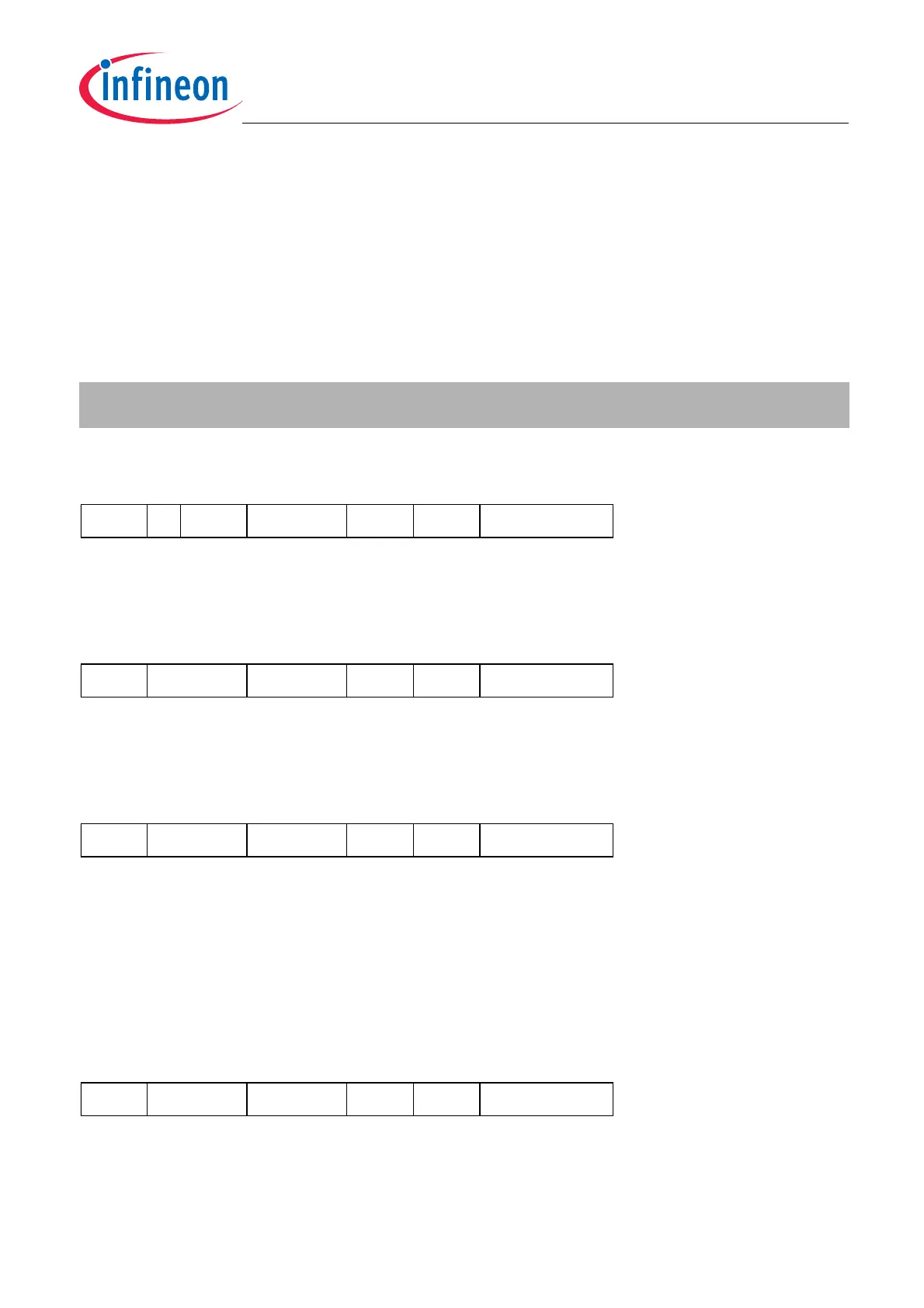

31

off10[9:6]

28 27

22

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

09

H

0

31

-

28 27

02

H

22 21

-

16 15

b

12 11

a

8 7

29

H

0

31

off10[9:6]

28 27

12

H

22 21

off10[5:0]

16 15

b

12 11

a

8 7

29

H

0

Loading...

Loading...