TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-342

SHA.H

Arithmetic Shift Packed Half-words

Description

If the shift count specified through the contents of either D[b] (instruction format RR) or const9 (instruction format

RC) is greater than or equal to zero, then left-shift each half-word in D[a] by the amount specified by shift count.

The vacated bits are filled with zeros and bits shifted out are discarded. If the shift count is less than zero, right-

shift each half-word in D[a] by the absolute value of the shift count. The vacated bits are filled with the sign-bit (the

most significant bit) of the respective half-word, and bits shifted out are discarded. Put the result in D[c]. Note that

for the shifts, each half-word is treated individually, and bits shifted out of a half-word are not shifted into the next

half-word.

The shift count is a signed number, derived from the sign-extension of either D[b][4:0] (format RR) or const9[4:0]

(format RC).

The range for the shift count is -16 to +15. The result for each half-word for a shift count of -16 is either all zeros

or all ones, depending on the sign-bit of the respective half-word.

SHA.HD[c], D[a], const9 (RC)

if (const9[4:0] >= 0) then {

result_halfword0 = D[a][15:0] << const9[4:0];

result_halfword1 = D[a][31:16] << const9[4:0];

} else {

shift_count = 0 - const9[4:0];

msk = D[a][31] ? (((1 << shift_count) - 1) << (16 - shift_count)) : 0;

result = msk | (D[a] >> shift_count);

result_halfword0 = msk | (D[a][15:0] >> shift_count);

result_halfword1 = msk | (D[a][31:16] >> shift_count);

}

D[c][15:0] = result_halfword0[15:0];

D[c][31:16] = result_halfword1[15:0];

SHA.HD[c], D[a], D[b] (RR)

if (D[b][4:0] >= 0) then {

result_halfword0 = D[a][15:0] << D[b][4:0];

result_halfword1 = D[a][31:16] << D[b][4:0];

} else {

shift_count = 0 - D[b][4:0];

msk = D[a][31] ? (((1 << shift_count) - 1) << (16 - shift_count)) : 0;

result_halfword0 = msk | (D[a][15:0] >> shift_count);

result_halfword1 = msk | (D[a][31:16] >> shift_count);

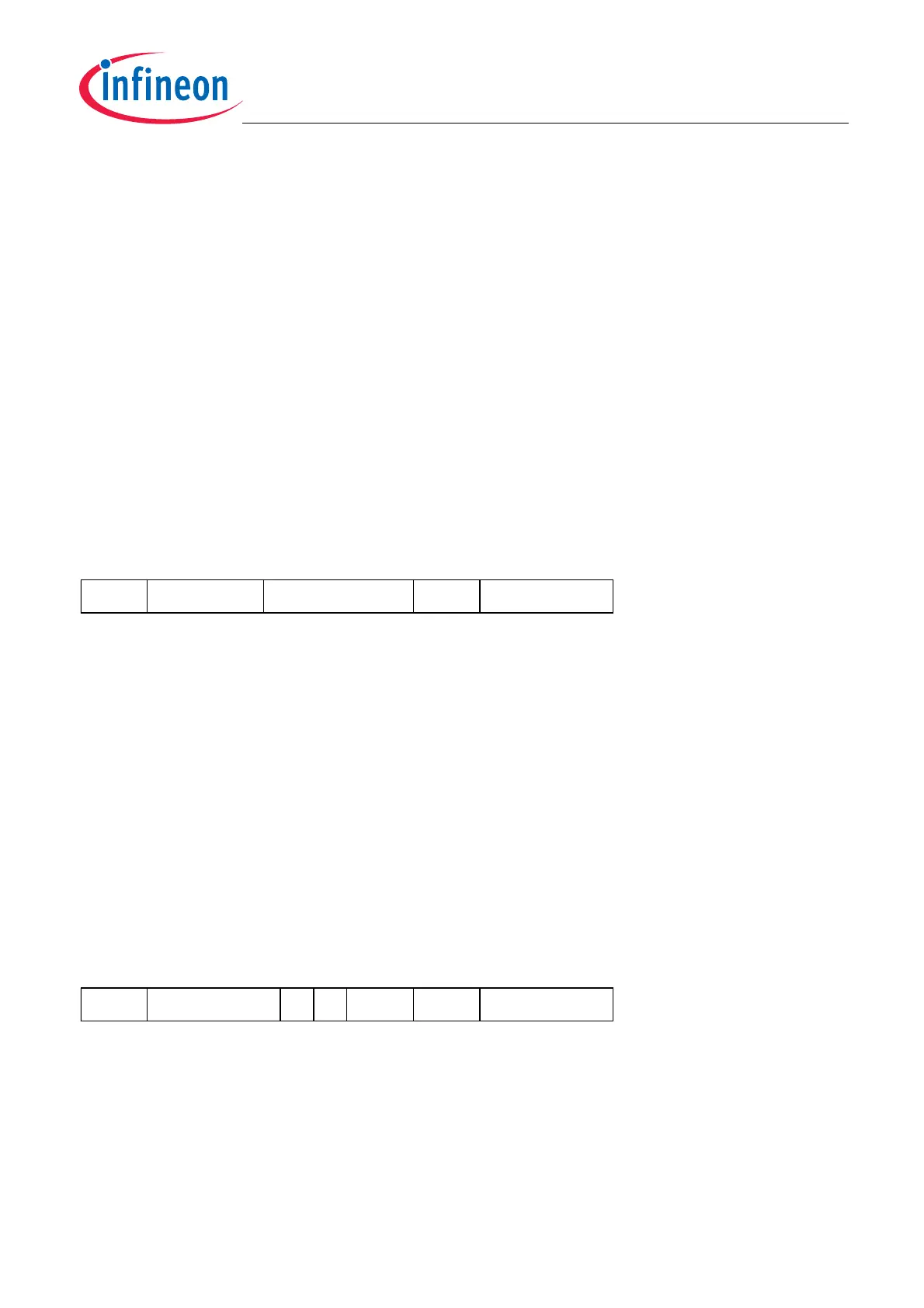

31

c

28 27

41

H

21 20

const9

12 11

a

8 7

8F

H

0

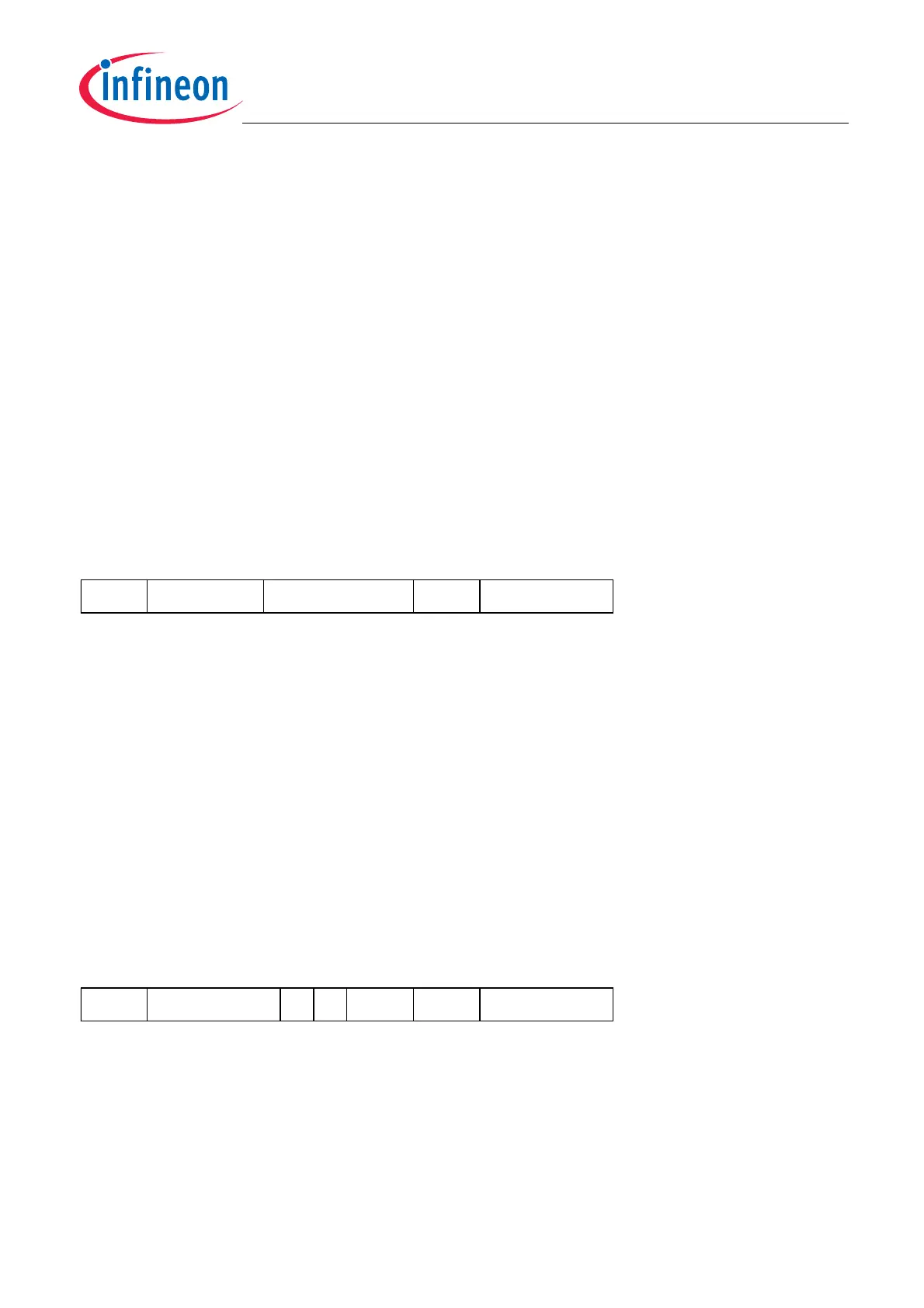

31

c

28 27

41

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0F

H

0

Loading...

Loading...