TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-24

ADDS.H

Add Signed Packed Half-word with Saturation

ADDS.HU

Add Unsigned Packed Half-word with Saturation

Description

Add the contents of each half-word of D[a] and D[b] and put the result in each corresponding half-word of D[c],

with saturation on signed overflow (ADDS.H) or saturation on unsigned overflow (ADDS.HU). The overflow

(PSW.V) and advance overflow (PSW.AV) conditions are calculated for each half-word of the packed quantity.

ADDS.HD[c], D[a], D[b] (RR)

result_halfword1 = D[a][31:16] + D[b][31:16];

result_halfword0 = D[a][15:0] + D[b][15:0];

D[c] = {ssov(result_halfword1, 16), ssov(result_halfword0, 16)};

ADDS.HUD[c], D[a], D[b] (RR)

result_halfword1 = D[a][31:16] + D[b][31:16]; // unsigned addition

result_halfword0 = D[a][15:0] + D[b][15:0]; // unsigned addition

D[c] = {suov(result_halfword1, 16), suov(result_halfword0, 16)};

Status Flags

C Not set by these instructions.

V ADDS.H

ov_halfword1 = (result_halfword1 > 7FFF

H

) OR (result_halfword1 < -8000

H

);

ov_halfword0 = (result_halfword0 > 7FFF

H

) OR (result_halfword0 < -8000

H

);

overflow = ov_halfword1 OR ov_halfword0;

if (overflow) then PSW.V = 1 else PSW.V = 0;

ADDS.HU

ov_halfword1 = (result_halfword1 > FFFF

H

) OR (result_halfword1 < 0000

H

);

ov_halfword0 = (result_halfword0 > FFFF

H

) OR (result_halfword0 < 0000

H

);

overflow = ov_halfword1 OR ov_halfword0;

if (overflow) then PSW.V = 1 else PSW.V = 0;

SV if (overflow) then PSW.SV = 1 else PSW.SV = PSW.SV;

AV aov_halfword1 = result_halfword1[15] ^ result_halfword1[14];

aov_halfword0 = result_halfword0[15] ^ result_halfword0[14];

advanced_overflow = aov_halfword1 OR aov_halfword0;

if (advanced_overflow) then PSW.AV = 1 else PSW.AV = 0;

SAV if (advanced_overflow) then PSW.SAV = 1 else PSW.SAV = PSW.SAV;

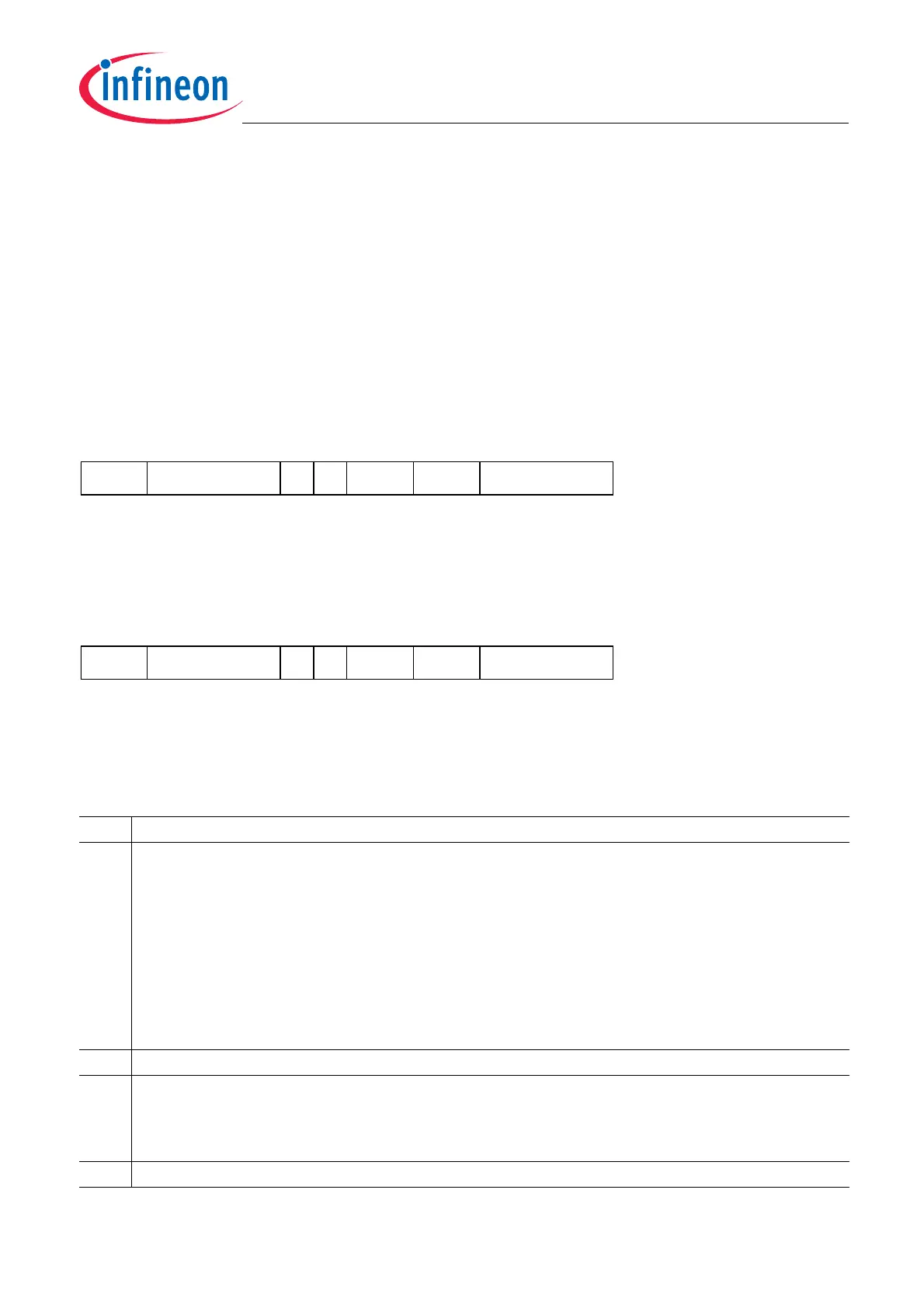

31

c

28 27

62

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0B

H

0

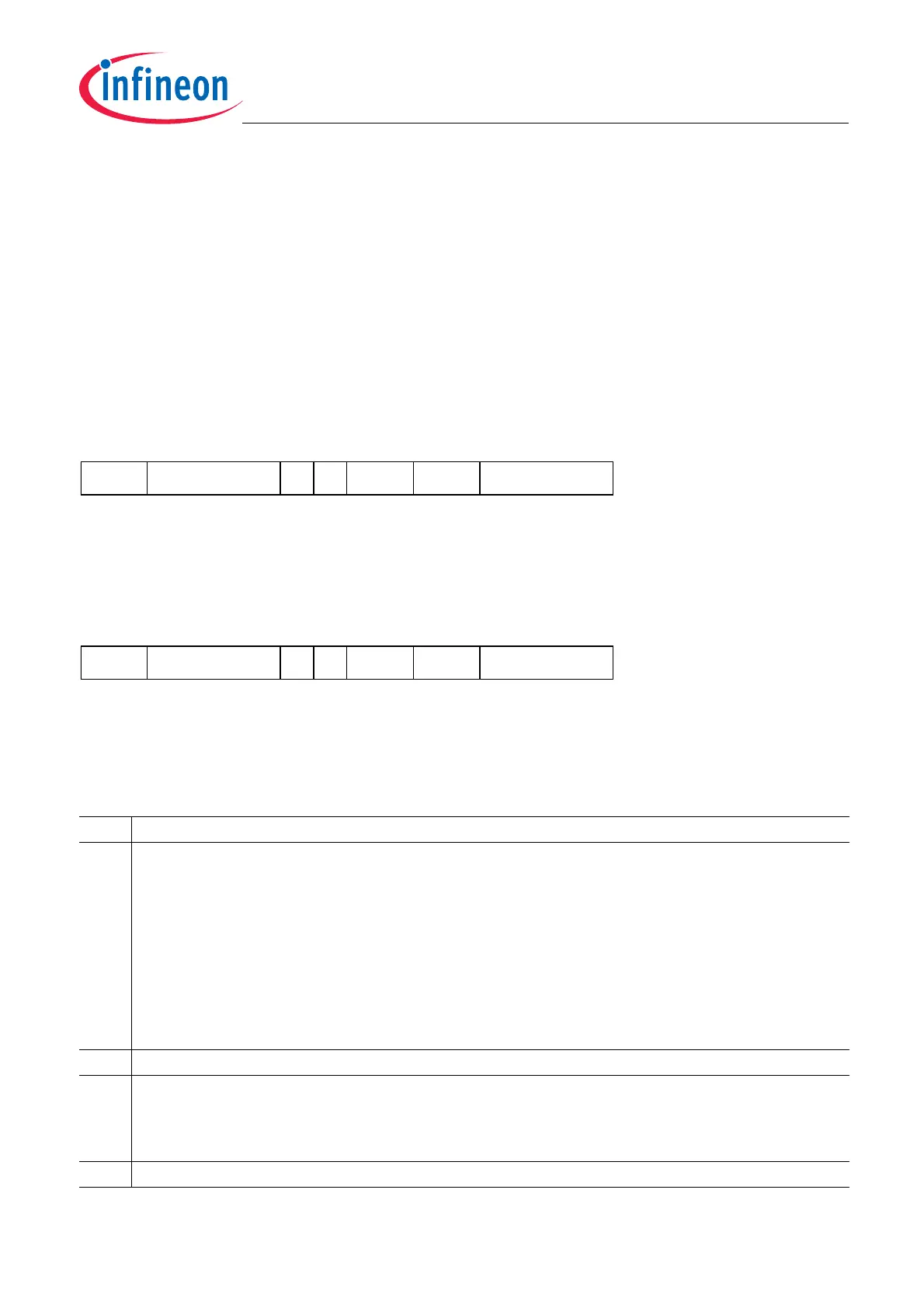

31

c

28 27

63

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0B

H

0

Loading...

Loading...