TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-30

AND

Bitwise AND

Description

Compute the bitwise AND of the contents of data register D[a] and the contents of either data register D[b]

(instruction format RR) or const9 (instruction format RC) and put the result in data register D[c]. The const9 value

is zero-extended.

ANDD[c], D[a], const9 (RC)

D[c] = D[a] & zero_ext(const9);

ANDD[c], D[a], D[b] (RR)

D[c] = D[a] & D[b];

ANDD[15], const8 (SC)

ANDD[a], D[b] (SRR)

Status Flags

Compute the bitwise AND of the contents of either data register D[a] (instruction format SRR) or D[15] (instruction

format SC) and the contents of either data register D[b] (format SRR) or const8 (format SC), and put the result

in data register D[a] (format SRR) or D[15] (format SC). The const8 value is zero-extended.

D[15] = D[15] & zero_ext(const8);

D[a] = D[a] & D[b];

C Not set by this instruction.

V Not set by this instruction.

SV Not set by this instruction.

AV Not set by this instruction.

SAV Not set by this instruction.

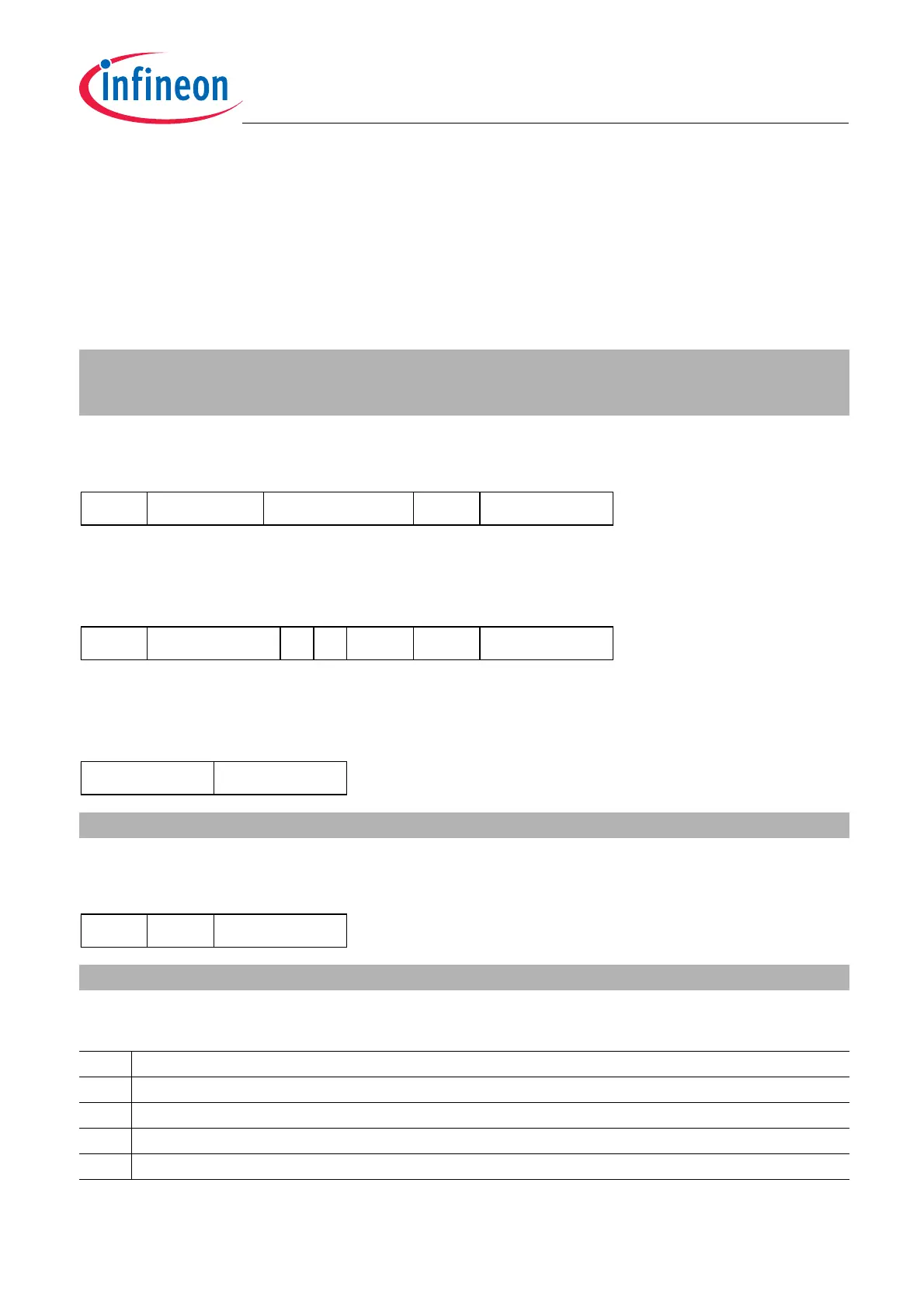

31

c

28 27

08

H

21 20

const9

12 11

a

8 7

8F

H

0

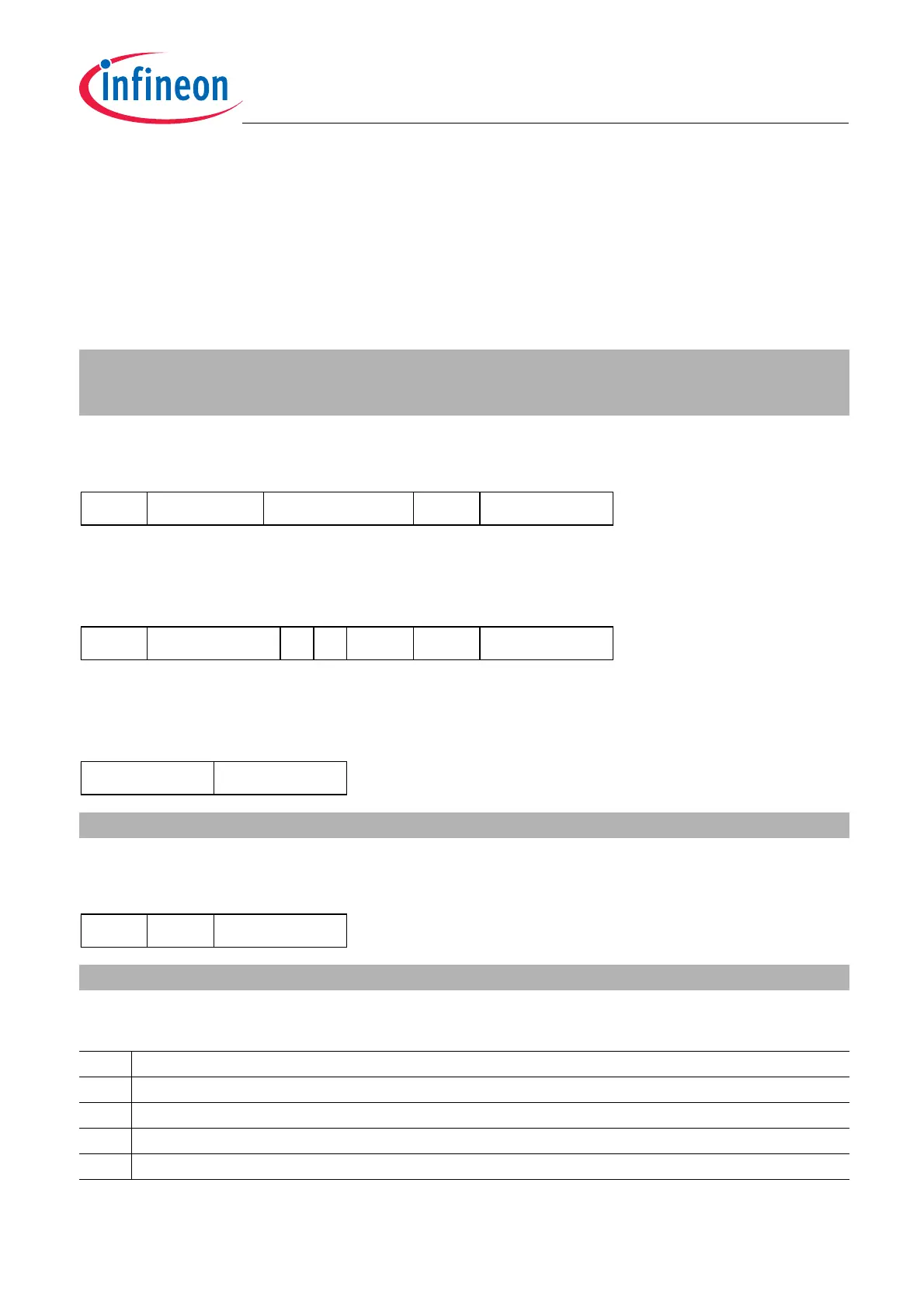

31

c

28 27

08

H

20 19

-

18 17

-

16 15

b

12 11

a

8 7

0F

H

0

Loading...

Loading...