TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set Overview

V1.0 2013-07

User Manual (Volume 2) 2-15

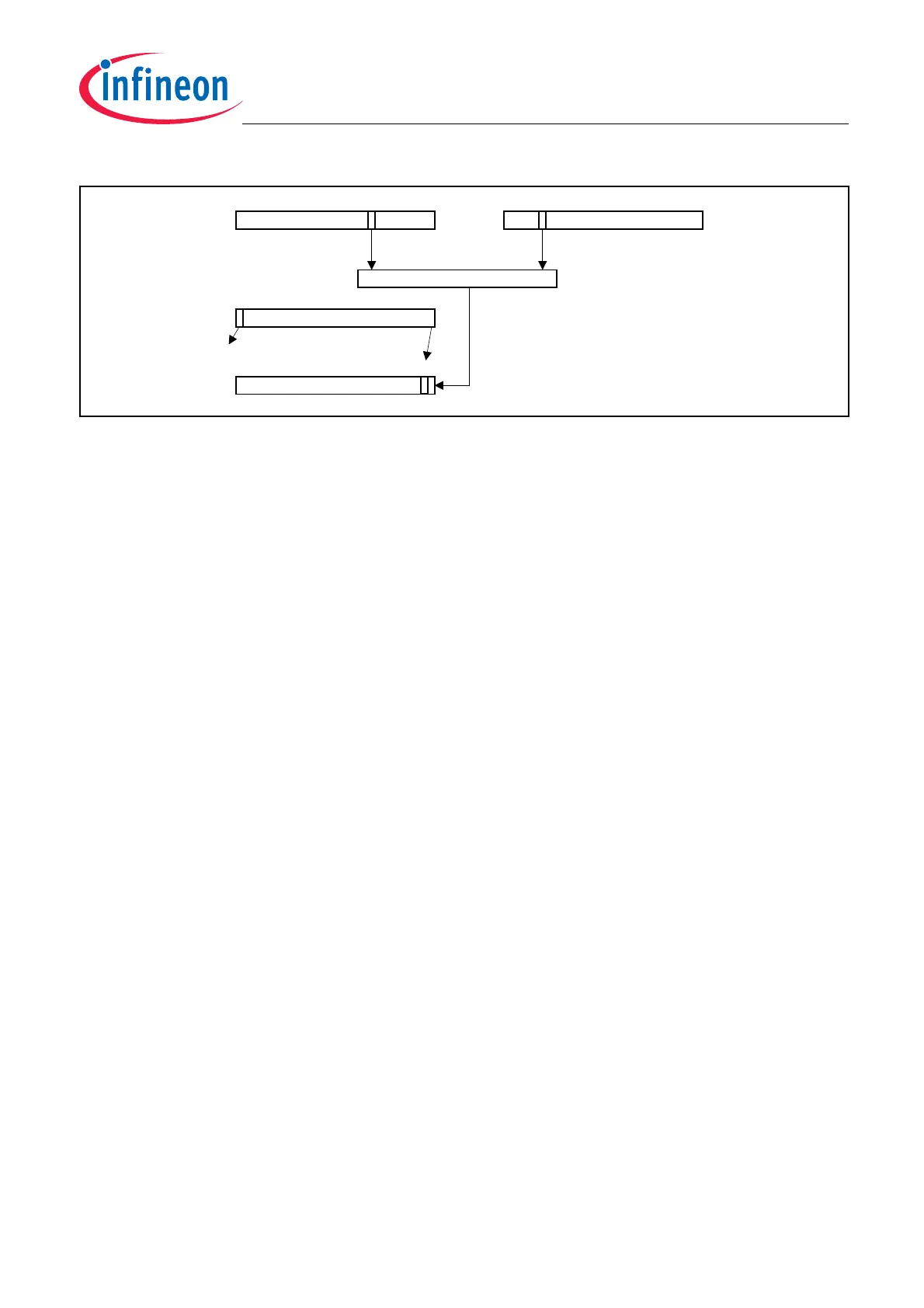

Figure 2-14 Shift Plus Boolean Operation

2.7 Address Arithmetic

The TriCore architecture provides selected arithmetic operations on the address registers. These operations

supplement the address calculations inherent in the addressing modes used by the load and store instructions.

Initialization of base pointers requires a constant to be loaded into an address register. When the base pointer is

in the first 16-KBytes of each segment this can be achieved using the Load Effective Address (LEA) instruction,

using the absolute addressing mode.

Loading a 32-bit constant into an address register is accomplished using MOVH.A followed by an LEA that uses

the base plus 16-bit offset addressing mode. For example:

movh.a a5, ((ADDRESS+8000

H

)>>16) & FFFF

H

lea a5, [a5](ADDRESS & FFFF

H

)

The MOVH.A instruction loads a 16-bit immediate into the most-significant 16-bits of an address register and zero-

fills the least-significant 16-bits.

A 16-bit constant can be added to an address register by using the LEA instruction with the base plus offset

addressing mode. A 32-bit constant can be added to an address register in two instructions: an Add Immediate

High-word (ADDIH.A), which adds a 16-bit immediate to the most-significant 16-bits of an address register,

followed by an LEA using the base plus offset addressing mode. For example:

addih.a a8, ((OFFSET+8000

H

)>>16) & FFFF

H

lea a8, [a8](OFFSET & FFFF

H

)

The Add Scaled (ADDSC.A) instruction directly supports the use of a data variable as an index into an array of

bytes, half-words, words or double-words.

2.8 Address Comparison

As with the comparison instructions that use the data registers (see Compare Instructions, page 2-11), the

comparison instructions using the address registers put the result of the comparison in the least-significant bit of

the destination data register and clear the remaining register bits to zeros.

An example using the Less Than (LT.A) instruction is shown in Figure 2-15:

D[a] D[b]

Boolean op

p1

D[c]

0

p2

D[c]

31 0 31 0

31

0

31

Discarded

Left Shift 1

TC1057B

12

op = AND, ANDN, NAND,

NOR, OR, ORN, XNOR or

XOR

Loading...

Loading...