TriCore

®

TC1.6P & TC1.6E

32-bit Unified Processor Core

Instruction Set

V1.0 2013-07

User Manual (Volume 2) 3-205

MADDR.Q

Multiply-Add Q Format with Rounding

MADDRS.Q

Multiply-Add Q Format with Rounding, Saturated

Description

Multiply two signed 16-bit (half-word) values, add the product (left justified if n == 1) to a 32-bit signed value, and

put the rounded result in a 32-bit register. The lower half-word is cleared. Overflow and advanced overflow are

calculated on the final results.

Note that n should only take the values 0 or 1, any other value returns an undefined result. If (n == 1) then 8000

H

* 8000

H

= 7FFFFFFF

H

(for signed 16-bit * 16-bit multiplications only).

MADDR.QD[c], D[d], D[a] L, D[b] L, n (RRR1)

32 + (16L * 16L) rounded --> 32

sc = (D[a][15:0] == 8000

H

) AND (D[b][15:0] == 8000

H

) AND (n == 1);

mul_res = sc ? 7FFFFFFF

H

: ((D[a][15:0] * D[b][15:0]) << n);

result = D[d] + mul_res + 8000

H

;

D[c] = {result[31:16], 16’b0}; // Short fraction

MADDR.QD[c], D[d], D[a] U, D[b] U, n (RRR1)

32 + (16U * 16U) rounded --> 32

sc = (D[a][31:16] == 8000

H

) AND (D[b][31:16] == 8000

H

) AND (n == 1);

mul_res = sc ? 7FFFFFFF

H

: ((D[a][31:16] * D[b][31:16]) << n);

result = D[d] + mul_res + 8000

H

;

D[c] = {result[31:16], 16’b0}; // Short fraction

MADDRS.QD[c], D[d], D[a] L, D[b] L, n (RRR1)

32 + (16L * 16L) rounded --> 32 saturated

sc = (D[a][15:0] == 8000

H

) AND (D[b][15:0] == 8000

H

) AND (n == 1);

mul_res = sc ? 7FFFFFFF

H

: ((D[a][15:0] * D[b][15:0]) << n);

result = D[d] + mul_res + 8000

H

;

D[c] = {ssov(result,32)[31:16]), 16’b0}; // Short fraction

MADDRS.QD[c], D[d], D[a] U, D[b] U, n (RRR1)

32 + (16U * 16U) rounded --> 32 saturated

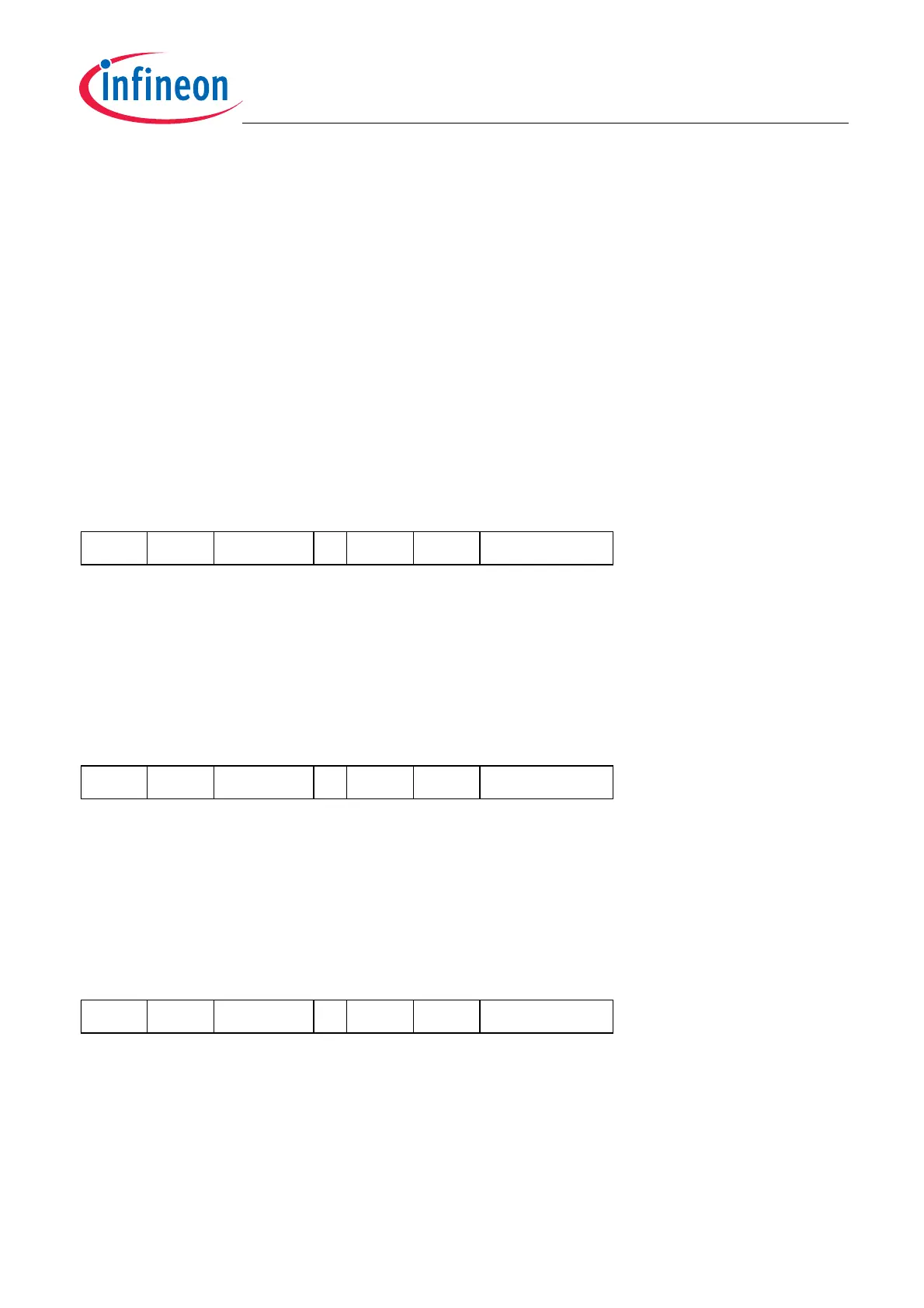

31

c

28 27

d

24 23

07

H

18 17

n

16 15

b

12 11

a

8 7

43

H

0

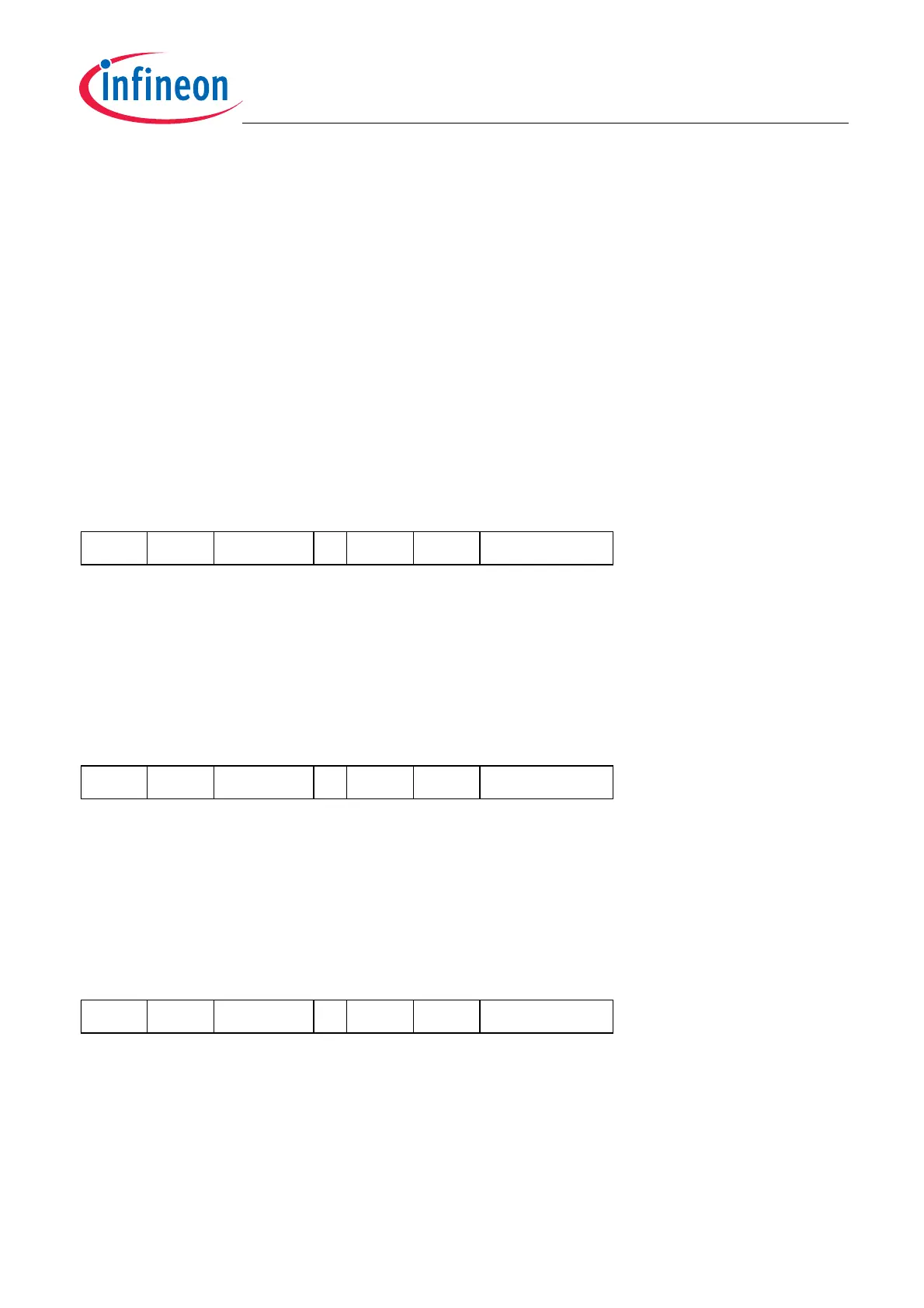

31

c

28 27

d

24 23

06

H

18 17

n

16 15

b

12 11

a

8 7

43

H

0

31

c

28 27

d

24 23

27

H

18 17

n

16 15

b

12 11

a

8 7

43

H

0

Loading...

Loading...